- 全部

- 默认排序

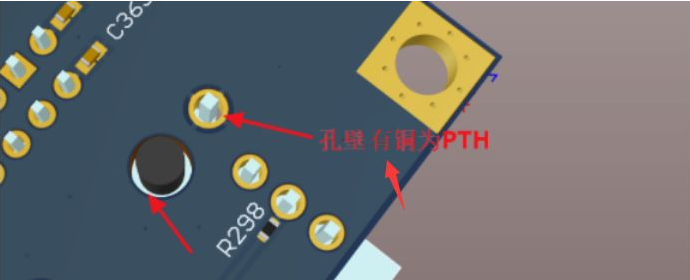

可以观察到电路板中有着许多大大小小的空洞,会发现是许多密密麻麻的小孔,每个孔洞都是有其目的而被设计出来的。 这些孔洞大体上可以分成 PTH(PLating Through Hole, 电镀通孔)及 NPTH(Non PLating Thro

C++编程习惯与编程要点

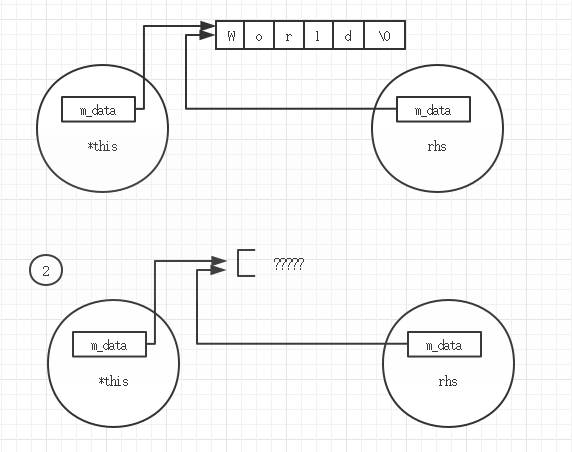

以良好的方式编写C++ class假设现在我们要实现一个复数类comPLex,在类的实现过程中探索良好的编程习惯。① Header(头文件)中的防卫式声明comPLex.h:# ifndef __COMPLEX__# define __COMPLEX__class comPLex{}# endif

C++代码提供了足够的灵活性,因此对于大部分工程师来说都很难把握。本文介绍了写好C++代码需要遵循的10个最佳实践,并在最后提供了一个工具可以帮助我们分析C++代码的健壮度。原文:10 Best practices to design and imPLement a C++ class1. 尽可能尝

初学者在学习PCB技术时,接触PCB板设计会学到网格状填充区和填充区,经常会将其混为一谈,其实这是错误的,这两者毫无关系,今天我们来讲讲他们的区别,并回答一些关于PCB技术的问题。1、网格状填充区(External PLane)和填充区(F

MX811-1F: Ex d IIB T6 Gb/ExtD A21 IP68 T80℃MX911-1F: Ex d IIC T6 Gb/ExtD A21 IP68 T80℃802.11a/b/g/n/ac, 1x 1G WAN port,

实际设计当中,经常需要对一些功能进行文字说明,或者对可选线路进行文字标注。这些文字注释可以大大增强线路的可读性,后期也可以让布线工程充分对所关注的线路进行特别处理。1、放置字符标注字符标注主要针对的是较短的文字说明。(1)执行菜单命令“PL

通常,在单独的代码段中执行计算的每个步骤是一种很好的编程实践,本文介绍如何从另一个宏中调用ZPL宏,以及如何在宏之间来回传递数据。 介绍 在编写执行许多步骤的ZPL宏时,通常在单独的代码段中执行每个步骤是一种良好的编程做法。这可以通过Z

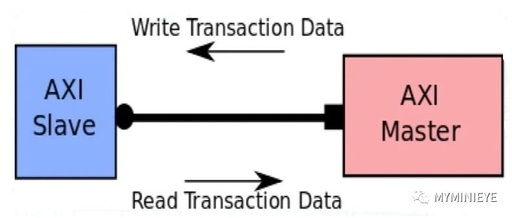

在Xinlinx的ZYNQ中,拥有ARM+FPGA这种架构,每款产品均带有双精度浮点的双核ARMCortex-A9MPCore处理系统,ARM(PS端)具有比较强的事务管理功能,可以用来跑界面以及应用程序等,其优势主要体现在控制方面,里面整合了很多现成的硬件资源供编程调用。FPGA(PL端)灵活性强

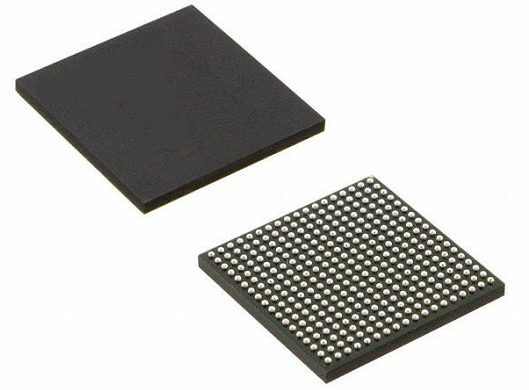

概述MAX V系列低成本和低功耗CPLD提供更大的密度和每占地面积的I/O。MAX V器件的密度从40到2210个逻辑元件(32到1700个等效宏单元)和多达271个I/O,为I/O扩展、总线和协议桥接、电源监控和控制、FPGA配置和模拟I

5M2210ZF256I5N CPLD MAX V设备器件特点;低成本、低功耗、非易失性CPLD架构即时启动(0.5 ms或更短)配置时间待机电流低至25µA,快速下电/复位操作快速传播延迟和时钟到输出时间内部振荡器模拟RSDS输出支持,数

扫码关注

扫码关注