- 全部

- 默认排序

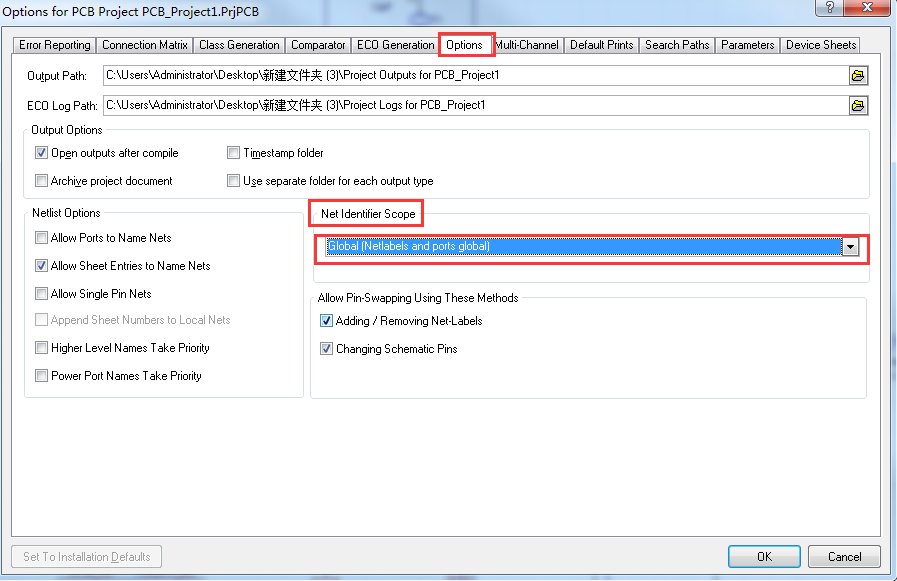

我们在日常画板子的时候,有时会出现一个比较尴尬的问题:同一个工程下不同原理图之间的相同网络标号导入到PCB文件之后,PIn没有连接在一起;编译是还会出现报错,error:Duplicate Net Names。可以直接忽略,但存在报错实在让人难受。

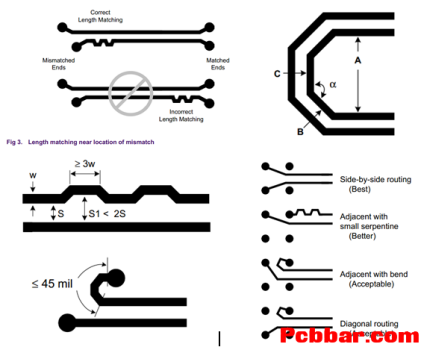

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

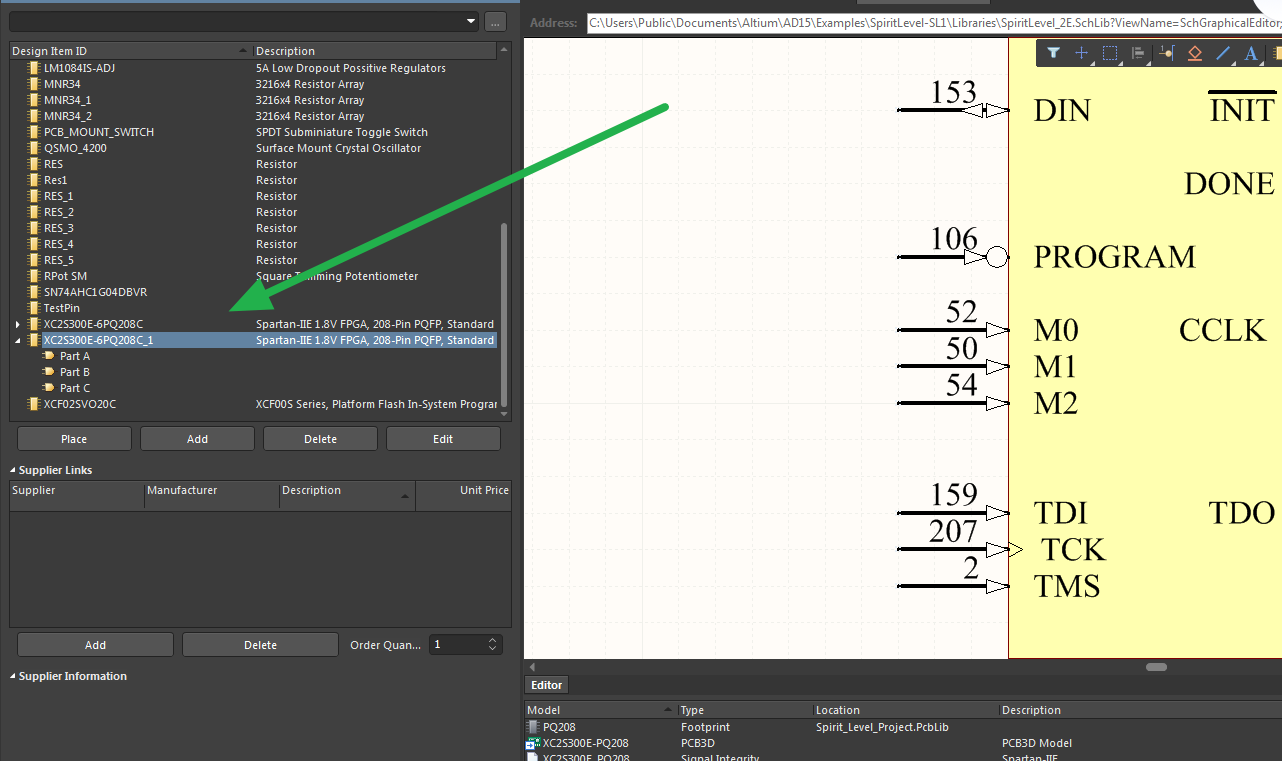

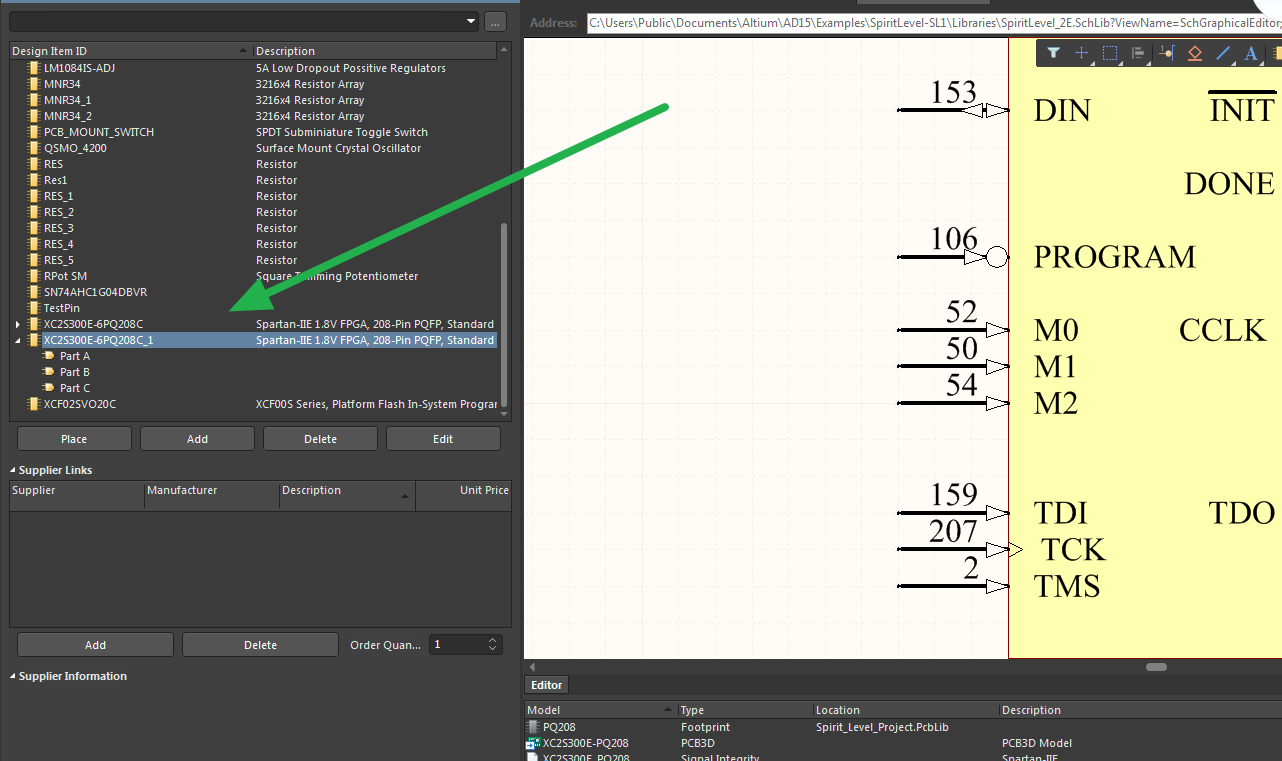

有时候我们会出现我们的原理图导入我们的PCB出现我们的导入不成功,并且检查封装都是ok,也没有出现unkown PIn,但是我们的PCb分封装就是导入不成功,这是由于我们的有时候在设计原理图的时候,我们会习惯和方便将我们的原理图的器件进行直接的拷贝处理,直接进行复制粘贴过来,这样就会出现我们的ID号码一模一样,就会导入我们的PCB发生冲突。

AD19出现[Error] XXX.Sch ComPIler Sheet-Entry XX not matched to Port at Xmil,Ymil问题的解决方法

AD19出现ComPIler Component U4 TL082 has unused sub-part

AD19关于 [Warning] SQ.SCH Extra PIn 1 in Normal of part 的解决办法

AD19出现ComPIler Component U4 TL082 has unused sub-part

扫码关注

扫码关注

![AD19出现[Error] XXX.Sch Compiler Sheet-Entry XX not matched to Port at Xmil,Ymil问题的解决方法](https://api.fanyedu.com/public/uploads/huodong/20200829/eb0d17e258e8f5d199a4cc2bc41699e3.png)

![AD19关于 [Warning] SQ.SCH Extra Pin 1 in Normal of part 的解决办法](https://api.fanyedu.com/public/uploads/huodong/20200831/72e5c28050c1dfccb9e2e5980ecaf45c.png)