- 全部

- 默认排序

Agilex™ FPGA 家族基于10纳米技术,可为各种计算密集型和带宽密集型应用提供定制加速和连接,同时提高性能并降低功耗。 Agilex™ FPGA 家族采用异构 3D 系统级封装 (SiP) 技术,集成了首款基于 10 纳米制程技术的

Arria® 10 GT FPGA 采用 20 纳米工艺,收发器性能在芯片到芯片通信中高达 25.78 Gbps,在背板通信中高达 12.5 Gbps,具有多达 115 万个等效逻辑单元。Arria® 10 GT FPGA优势收发器带宽提升

Arria® 10器件系列包括高性能,低功耗的20 nm中端FPGA和SoC。Arria® 10器件系列实现了:比上一代中高端FPGA更高的性能。通过一套综合节能技术来降低功耗。Arria® 10器件专为各领域中高性能、功耗敏感的中端应用而

Arria® 10 GX是性能最高的中端 20-nm FPGA,具有96个全双工收发器,支持17.4Gbps芯片到芯片数据速率。此外,该FPGA还提供高达 12.5 Gbps 的背板数据传输速率以及多达 115 万个等效逻辑单元。Arria

自从人工智能(AI)大模型的横空出世,人们开始意识到算力的重要性,算力是计算能力的简称,算力实现的核心是CPU、GPU、FPGA、ASIC等各类计算芯片,并由计算机、服务器、高性能计算集群和各类智能终端等承载。可以说,谁的算力最多最强,就意

在现代电子与计算机技术领域,ARM、DSP及FPGA是最为常见且应用广泛的芯片技术,它们各自拥有独特的优势及应用场景,本文将针对这三种技术进行介绍,希望对小伙伴们有所帮助。1、ARM是什么?ARM(Advanced RISC Machine

随着工艺技术不断发展,芯片规模及复杂度翻倍增长,验证对芯片设计的重要性不言而喻,因为在芯片开发过程中,直接流片的成本让人望而却步。因此,工程师及厂商必须在流片前对芯片设计进行“原型验证”——就是模仿真实软件应用条件下的芯片和系统表现是否满足

1. 请问:对于找工作刷题,怎么看?热身有必要,但是规劝一句:题目是刷不完的。面试通过了,后面还得再工作15年。你咋刷?得想的长远些。做题不是终点。刷题,面试为了啥?建议刷题是补充,平时多积累数字IC/FPGA设计知识、技能。相关知识、技能见:zhuanlan.zhihu.com/p/352. 研究

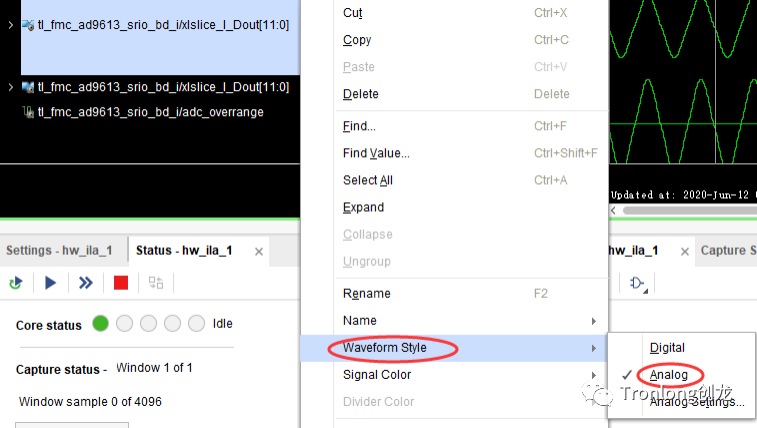

1案例说明1. Kintex-7 FPGA使用SRIO IP核作为Initiator,通过AD9613模块采集AD数据。AD9613采样率为250MSPS,双通道12bit,12bit按照16bit发送,因此数据量为16bit * 2 * 250M = 8Gbps;2. AD数据通过SRIO由Kin

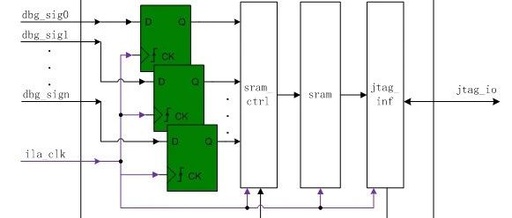

1. 前言在数字IP/IC,FPGA项目的上板验证阶段,对于一些难以确定原因的bug,比如:RTL仿真时,测试pattern覆盖不够全面,fPGA跑起来后的实际信号时序可能跟RTL 仿真不一致,从而出现Bug。一种debug的方式就是用FPGA工具提供的ILA模块(xilixn在ISE中叫:chip

扫码关注

扫码关注