- 全部

- 默认排序

答:ICT (In Circuit Tester,自动在线测试仪)是印制电路板生产中重要的测试设备:用于焊接后快速测试元器件的焊接质量,能迅速定位焊接不良的引脚,以便及时进行补焊。体现在PCB设计上,则需要在设计中添加用于ICT测试的焊盘,并对符合测试点要求的焊盘添加测试点属性。因测试点焊盘和间距及位置有严格的要求,对于有ICT设计要求的板卡,建议在设计前就明确添加ICT的网络,拟定ICT的添加计划,在设计的过程中边布线边添加。如果在设计完后再添加ICT测试点,必将大量返工,甚至有的网络根本无法

答:在使用动态铜皮的时候,会出现对铜皮进行Update to SmoOTh完了,还存在Out of date shapes的现象,如图6-332所示:

Silkscreen,指的是PCB设计中的丝印,包括TOP与BOOTOM面的丝印,正反面的丝印刚好是镜像过的。丝印一般包括器件的外框丝印线、IC器件的1脚标识、位号字符、有极性器件的极性标识。

(1)首先我们在进行TRIAC其驱动电路设计的时候,我们一般不直接进行驱动,而是通过DIAC或者PhOTo-TRIAC即光学的双向可控硅配合来使用进行驱动电路的设计,为什么呢?

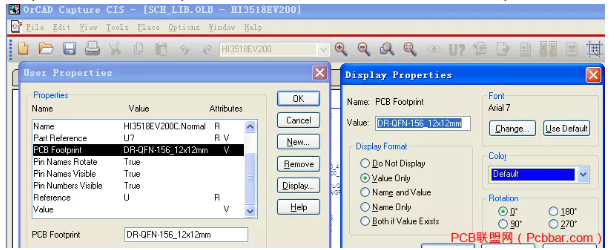

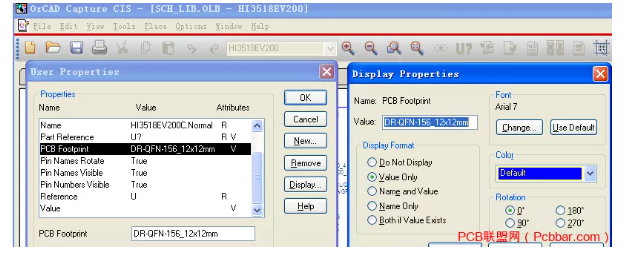

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB FoOTprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB FoOTprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

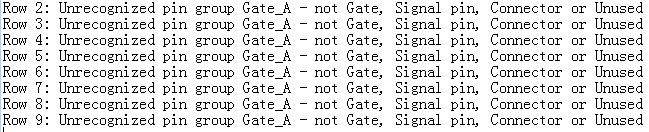

Row 2: Unrecognized pin group Gate_A - nOT Gate, Signal pin, Connector or Unused 在创建很多管脚的一个原理图封装的时候,一般会用到Excel表格去创建,这样就会省去不少时间去一个一个字码上去。

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB FoOTprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB FoOTprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

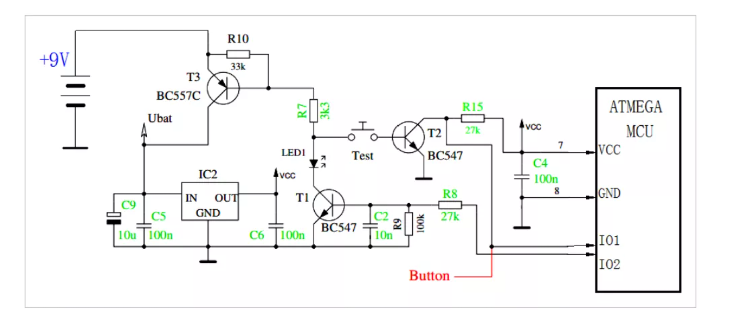

在电路上电之前。开关&quOT;TEST&quOT;断开,单片机也没有通过VCC加电。此时,T1的基极通过R9(100k)接地,处于截止状态。T3的基级电阻R7所连接的Test,T1都处于截止状态,所以T3也处于截止状态。

AD在制作原器件封装的时候旋转原器件管脚的方法,其实是有俩种的。第一种:选中双击管脚弹出属性编辑界面,如图1所示。在ROTation的选项下既可选中管脚的角度。图1第二种:选中管脚在拖动的状态下按空格键既可完成角度旋转。

第一步:创建好了封装之后,在SCH Library界面下面点击选择编辑命令。如图1所示图1第二步:点击编辑命令以后弹出原件编辑属性框,如图2所示点击“Parameters--Add--FoOTprint”图2第三步:点击以后,弹出一个对话框

扫码关注

扫码关注