- 全部

- 默认排序

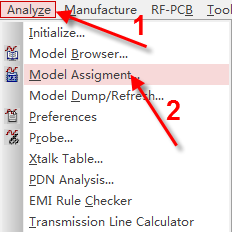

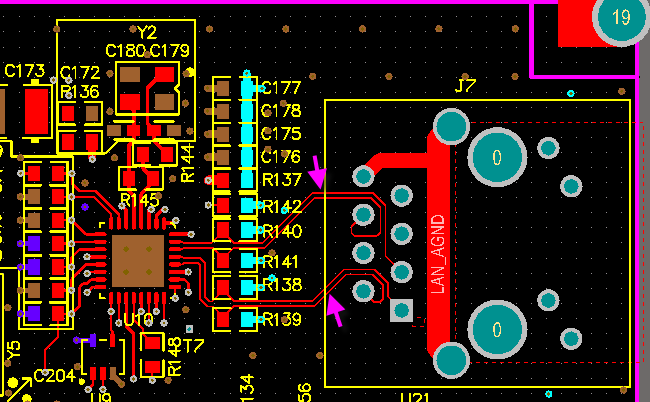

所谓的XNet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行XNet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用XNet就可以非常方便的实现这一功能,在Allegro软件中添加xNet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

以太网(EtherNet)是一种计算机局域网组网技术,该技术基于IEEE制定的IEEE 802.3标准,它规定了包括物理层的连线、电信号和介质访问层协议的内容。 以太网是当前应用最普遍的局域网技术。EtherNet的接口是实质是MAC通过MII总线控制PHY的过程。

现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:第一步,选中原理图根目录,执行菜单命令Tools-Create Netlist,创建网表,如图6-26所示; 图6-26 使用Orcad软件创建第一方网表示意图第二步,执行上述命令之后,会弹出如图6-27所示的界面,在此界面中选择PCB Editor,进行第一

[导读] EMC( ElectromagNetic Compatibility) 电磁兼容性对于一个产品而言是一个非常重要的性能指标,一个产品遇到EMC的坑,很多测试很难通过,很多软件同学可能会觉得EMC更多的是硬件攻城师要去应对的难题,与软件没毛关系。

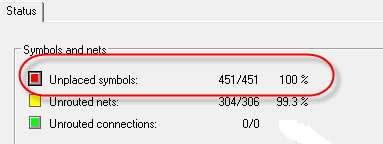

很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:第一步,需要检查原理图的网表是否导入成功,执行菜单命令Display,在下拉菜单中选择Status,整个PCB文件的状态,如图324-1所示,进入到状态的界面,最上面一栏是Symbols and Nets的选项,网表导入成功

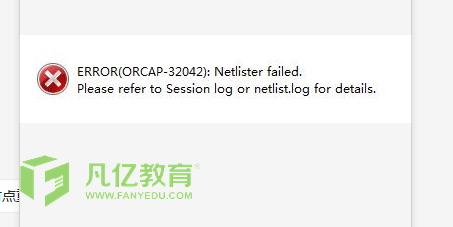

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

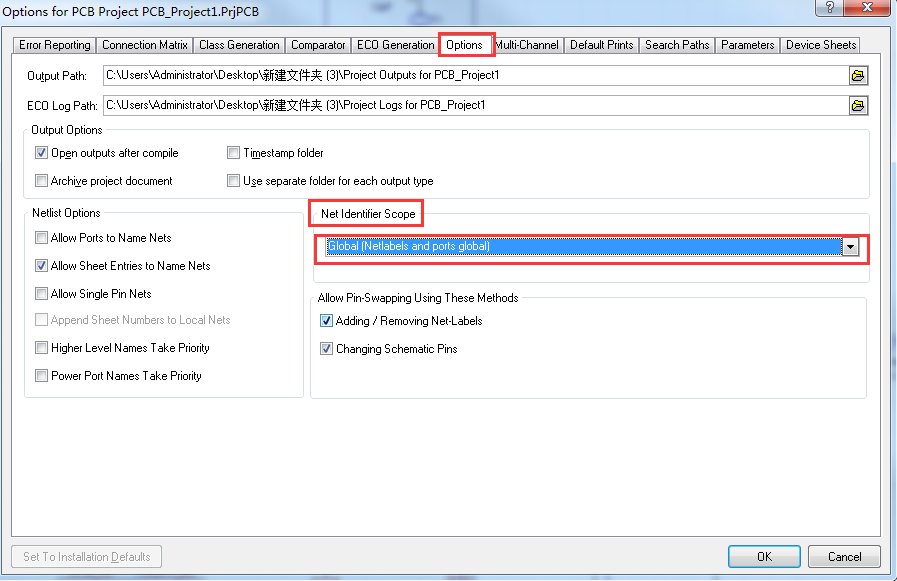

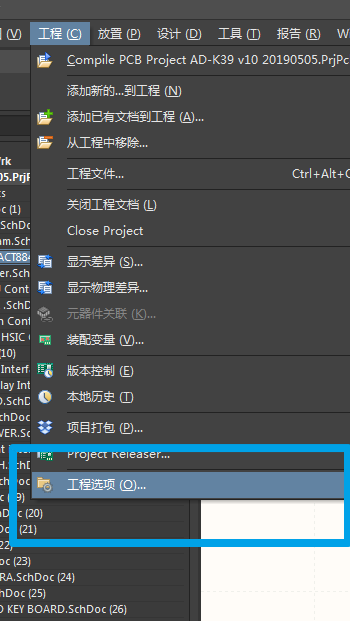

我们在日常画板子的时候,有时会出现一个比较尴尬的问题:同一个工程下不同原理图之间的相同网络标号导入到PCB文件之后,pin没有连接在一起;编译是还会出现报错,error:Duplicate Net Names。可以直接忽略,但存在报错实在让人难受。

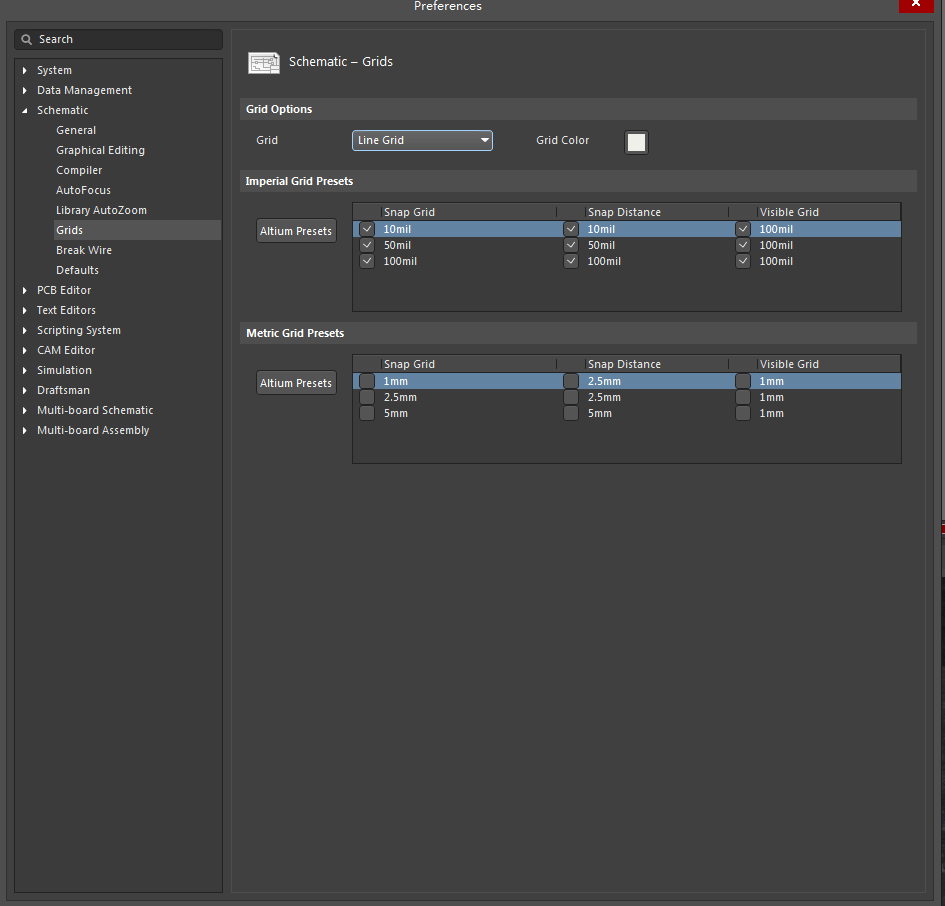

多通道入口参数的确认,首先我们知道我们的连接的通道的关系有几下几个,一个是通过Sheet Entry页连接符,一个是通过Port连接符号,还有一个是我们的NetLabel.

扫码关注

扫码关注