- 全部

- 默认排序

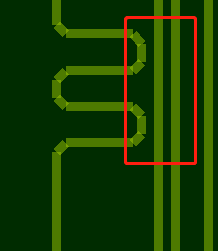

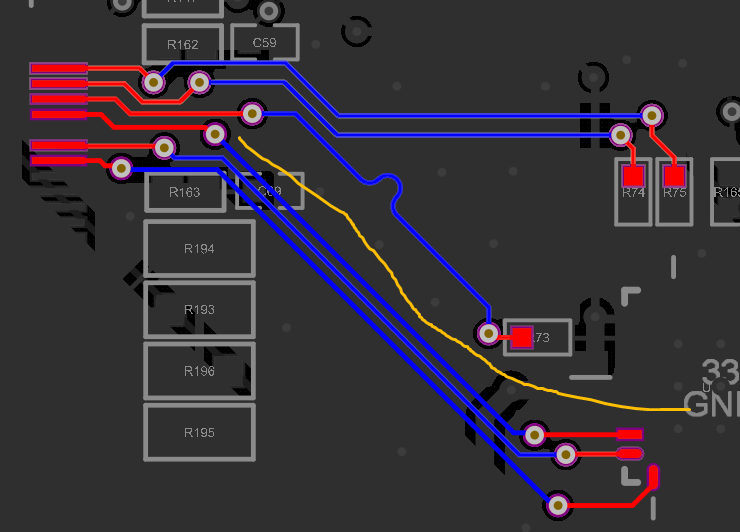

数据线线距不满足3w这里差分等长间距不能大于2Svref离数据线太近了以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ITem.taobao.com/ITem.ht

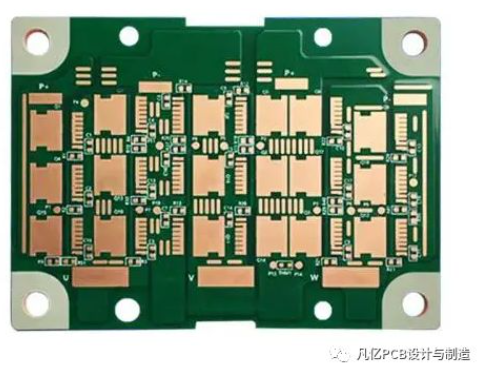

在当今世界,清洁能源和能源储存领域正在迅速崛起,储能市场正处于蓬勃发展的时期。这一趋势在可再生能源的普及和电动汽车行业的崭露头角的推动下得到了进一步的加速。随着市场需求的急剧攀升,储能PCB(Printed CircuIT Board,印刷

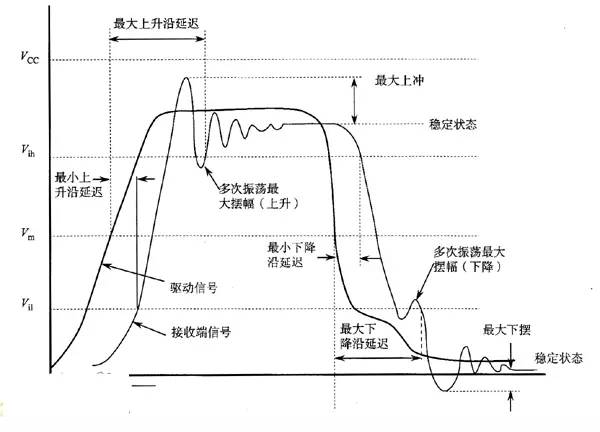

信号完整性的定义定义:信号完整性(Signal IntegrITy,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号

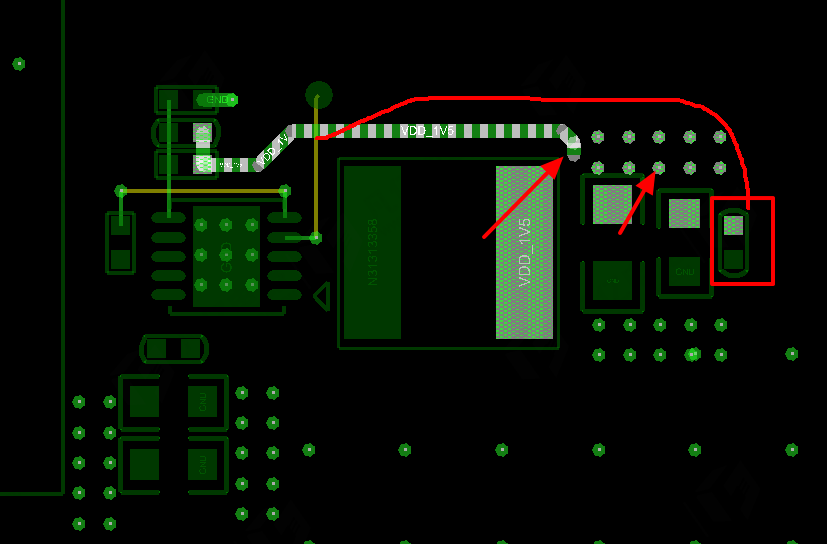

电源管脚拉出来之后加粗到15MIL:HDMI差分组 组内等长以及组跟组等长误差没问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ITem.taobao.co

在PCB(Printed CircuIT Board)制造过程中,表面处理是一个非常重要的步骤。表面处理可以提高PCB的可焊性、耐腐蚀性和可靠性,同时也可以增加PCB的外观质量。根据不同的需求,PCB表面处理工艺可以分为多种类型。在本文中,

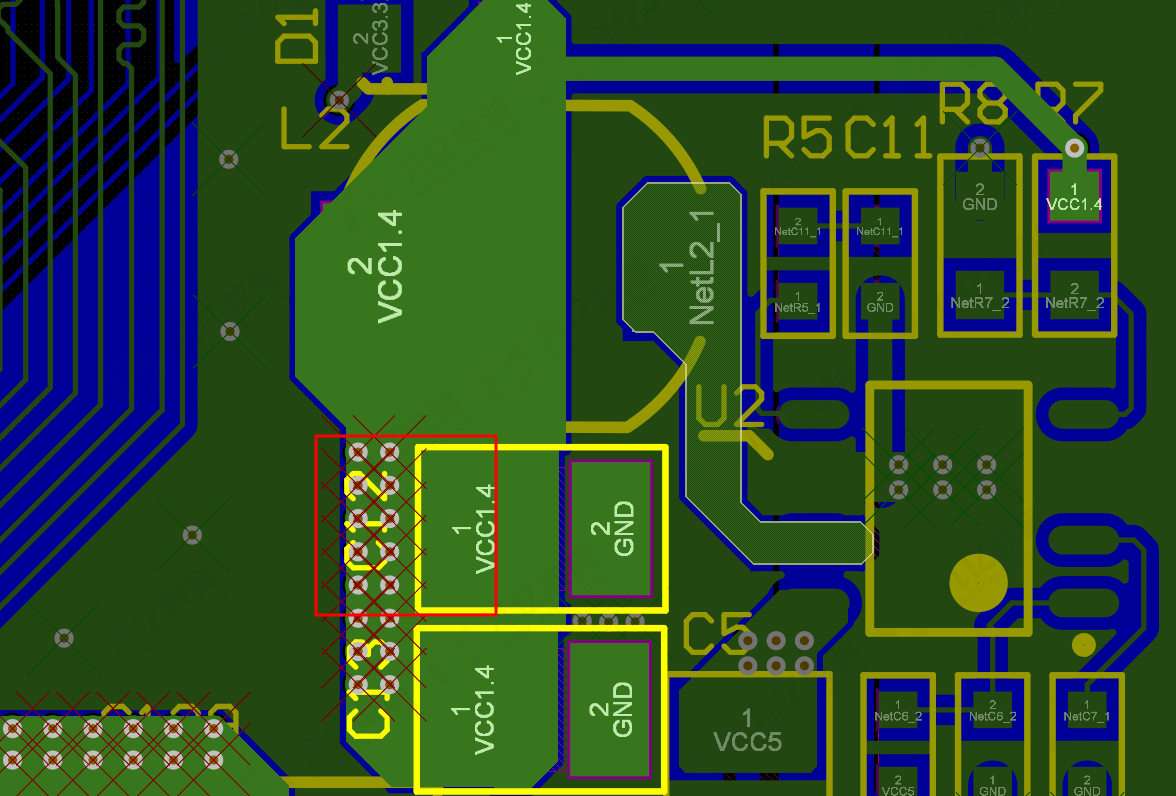

电源输出应打孔到最后一个器件后方器件摆放干涉,电容到芯片要保留一些间距,不能靠的太近以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ITem.taobao.com/

芯片的物理实现过程中不是所有的走线与器件都不是理想的。金属走线与金属走线有重叠有并行。器件也是周围也会有其他器件,或其他走线。最终都会引入额外的电容。就像在电路上额外多出来一些小的电容。无法避免。同样所有导电材料也会有电阻的特性。所以电路中

电源反馈信号要从最后一个器件连线,过孔要打到最后一个器件后方焊盘出线避免从长边出线布线保持3w间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ITem.ta

第三次作业

rx和tx之间要用gnd间隔差分对内等长误差大于+-5mil变压器旁边的线宽要大于20mil以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ITem.taobao.

大家过年好,你们的老朋友小Q又回来了,最近一段时间忙于公司项目开发,又加上过年比较忙,所以没能留出时间更新内容,大家是不是有点着急了?公司最近在使用jeesITe4开发项目,我呢,对这个框架一点也不熟悉,遇到问题都是现查现用。这不,在上传文件与上传图片这直接给卡死了。百度google了好久也没能找到

扫码关注

扫码关注