- 全部

- 默认排序

平时通过走路穿衣等日常活动带来的摩擦,会产生不同幅值的静电电压,但其能量很小不会对人体产生伤害,不过对于电子元器件来说,这种静电能量却是不能忽视的。在干燥的环境下,人体静电(ESD)的电压很容易超过6~35Kv,当用手触摸电子设备、PCB或

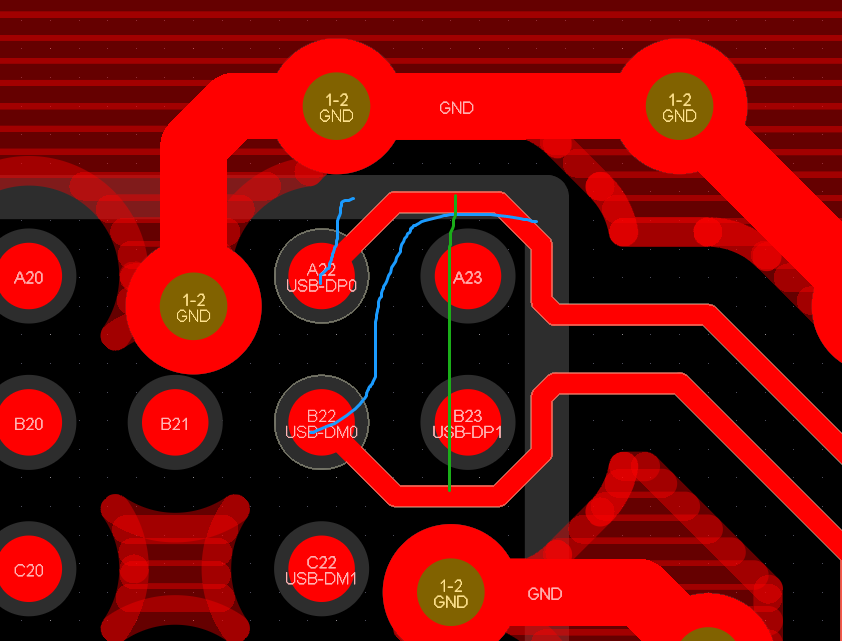

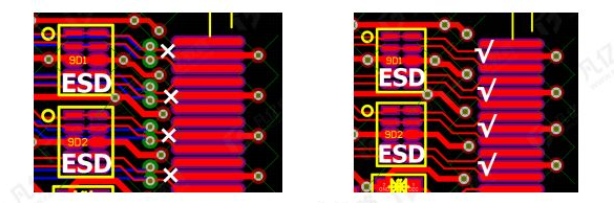

usb2.0差分出线要尽量耦合,你这个走线不满足差分间距规则电源走线需要加粗,或者铺铜处理3.0锯齿状等长不能超过线距的两倍,等长都需要再进行优化一下2.差分出线要尽量耦合3.打孔要打在ESD器件前面,先经过过孔,在到ESD器件4.地网络需

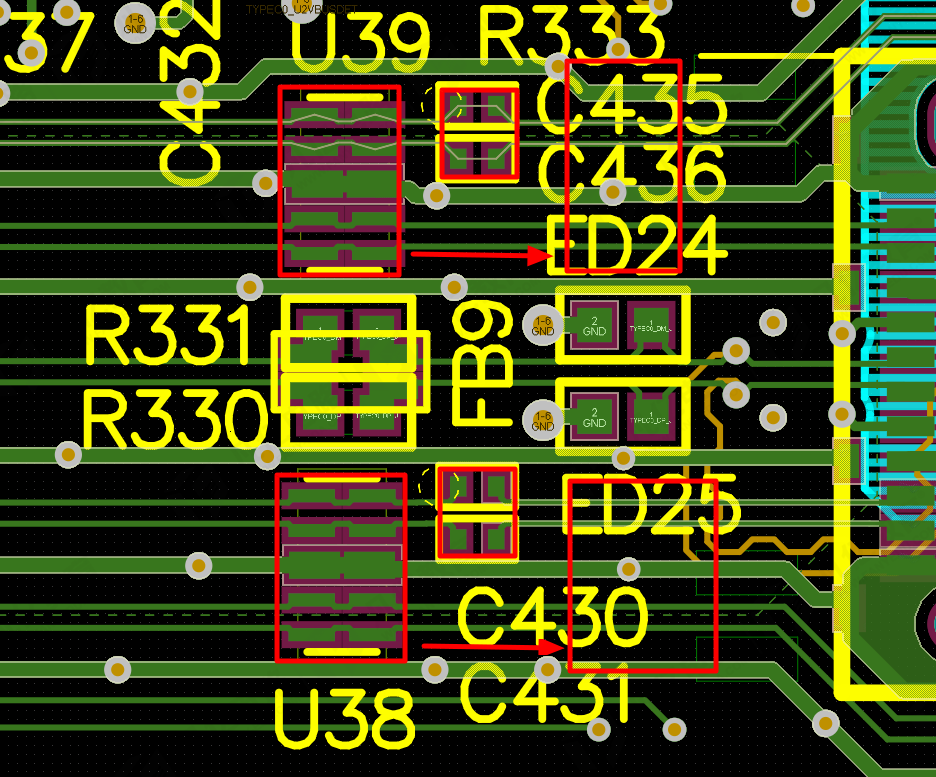

1.ESD器件应该尽量考近USB接口,放置的顺序是ESD-共模电感-阻容。2.差分对内等长误差控制在5mm以内。3.差分走线尽量保持在一层走线,避免一层走一半,换层在两端完成。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

一、MOS管输入电阻很高,为什么一遇到静电就不行了?MOS管一个ESD敏感器件,它本身的输入电阻很高,而栅-源极间电容又非常小,所以极易受外界电磁场或静电的感应而带电,又因在静电较强的场合难于泄放电荷,容易引起静电击穿。静电击穿一般分为两种

存在开路2.此处走线可以在进行一下优化3.器件摆放尽量中心对齐处理4.一层连接可以不用打孔5.差分需要进行对内等长,误差5mil6.ESD器件尽量靠近管脚摆放7.后期自己把电源和地再平面层处理一下,添加上网络以上评审报告来源于凡亿教育90天

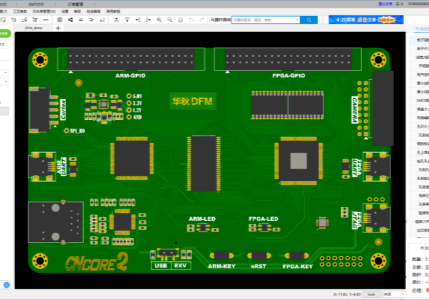

在PCB的布局设计中,元器件的布局至关重要,它决定了板面的整齐美观程度和印制导线的长短与数量,对整机的可靠性有一定的影响。一块好的电路板,除了实现原理功能之外,还要考虑EMI、EMC、ESD(静电释放)、信号完整性等电气特性,也要考虑机械结

静电放电(ESD)是在电子产品和PCB设计中常见的问题之一,若是处理不当,极有可能对电子元件和线路板造成永久性伤害,降低产品的可靠性,因此很多工程师遇见PCB板有ESD现象就要着手处理。1、为什么会产生静电放电现象?首先,了解ESD的来源是

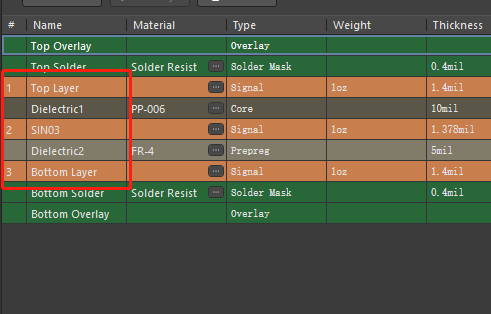

层叠一般都是双数,一般是4层,6层增加,高速信号都需要有完整的参考平面的2.差分走线注意要满足差分间距要求3.CC1和CC2属于重要信号管脚,走线需要加粗处理,ESD器件尽量靠近管脚摆放4.存在多处开路报错5.差分注意能顶层连通的就不用打孔

ESD:Electro-Static discharge的简称,意思是“静电释放”。静电是一种自然现象,通常通过接触、摩擦、电器间感应等方式产生,其特点是长时间积聚、高电压(可以产生几千伏甚至上万伏的静电)、低电量、小电流和作用时间短的特点

EMC:Electro Magnetic Compatibility的简称,也称电磁兼容,各种电气或电子设备在电磁环境复杂的共同空间中,以规定的安全系数满足设计要求的正常工作能力。本章对于 RK3588产品设计中的 ESD/EMI防护设计及

扫码关注

扫码关注