- 全部

- 默认排序

在电子元器件的可靠性测试中,DPA(Design and Process Audit)和FA(Failure Analysis)是两种重要的分析和测试方法。它们各自的定义和作用如下:DPA(Design and Process Audit)

电子工程师,第一次接触多层PCB板时,动辄十层八层的,线路像蜘蛛网一样,密密麻麻的,很容易看晕。甚至相比单双面板,多层板的设计难度是随着层数的增加,翻倍增长。8层PCB板的基本结构是由6个内部层和2个外部层组成,每一层都有其独特的功能,比如

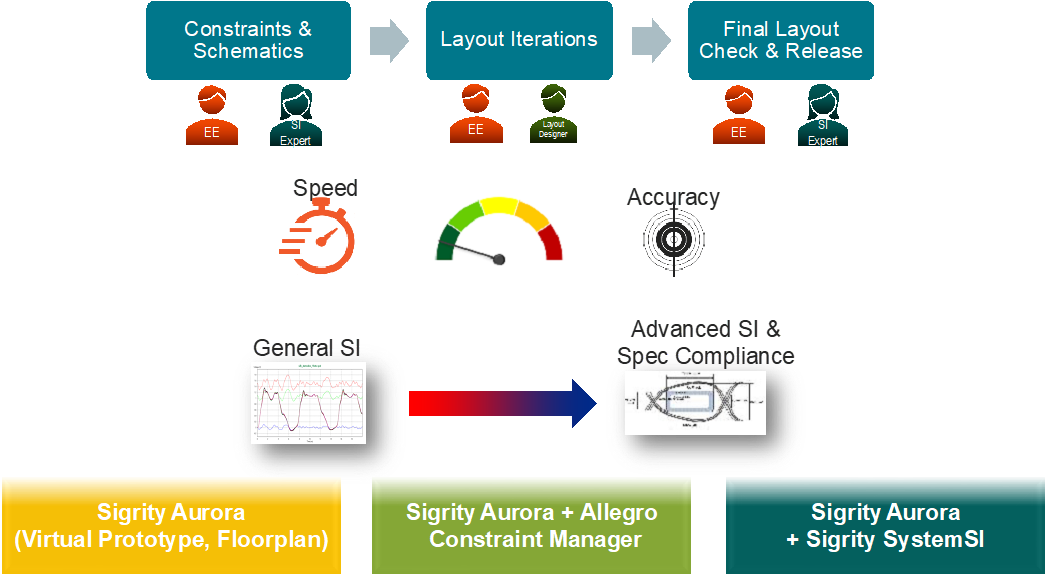

本文作者为 Cadence Design Systems 产品管理组总监 Brad Griffin,文章首发于 iconnect007.com。预计阅读时长:18分钟本文将重点介绍如何在无需久等 SI 和 PI 专家反馈的情况下,助力 PCB 设计团队在预算范围内按时交付合格的产品。对于当今设计高速

全球分布的设计团队越来越多,使缩短设计周期的难题雪上加霜。人工处理多用户问题的权宜措施非常耗时、缓慢并且容易出错。在PCB设计过程中遇到比较复杂的设计时候,通常需要我们进行协同设计,协同设计分为主设计者这以及从设计者,采用的是Allegro软件自带的Team Design功能,Team Design

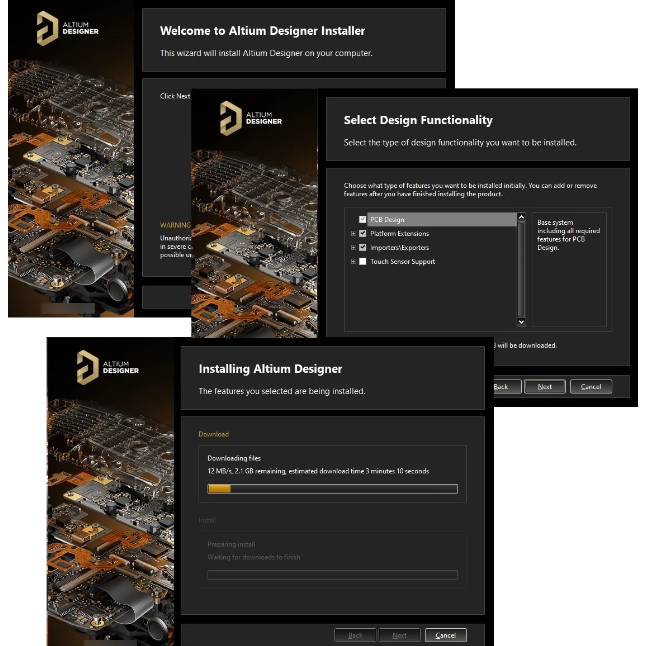

Altium Designer是由Altium公司推出的一款功能强大的专业的整的端到端电子印刷电路板设计环境,适用于电子印刷电路板设计。可以编辑原理图并在同一软件应用程序中布置印刷电路板。您还可以在同一环境中创建组件,配置各种输出文件,甚至

用Design Entry CIS生成逻辑网表的时候没有报错,能够成功的生成pxlBA.txt,netlist.log,pstchip.dat,pstxnet.dat,pstxprt.dat五个文件,这五个文件在同一个文件夹NetList下。然后一个叫work2的文件夹使用PCB Design GX

在Pcb Editor中已经创建了flash symbol,而且在路径下也能找到刚刚创建的flash symbol,但是用Pad Designer创建时在该路径下找不到刚刚创建的flash symbol,路径已经改了,但是还是找不到

小弟在github上下载了一个开源项目,但是其中的.brd文件无法打开,提示信息如下this Design is corrupted.it may have been copied form a different architecture using ASCII code;copy using b

如标题所述:AltiumDesigner17版怎么来设置铺铜到板框和与走线间的不同距离设置?同一个网络铺铜: 要求1:铺铜到板框的距离0.15mm要求2:铺铜到其它走线的距离是0.3mm要怎么设置啊(最好有祥细的图文步骤),求各位大神支招,感激不尽。

扫码关注

扫码关注