- 全部

- 默认排序

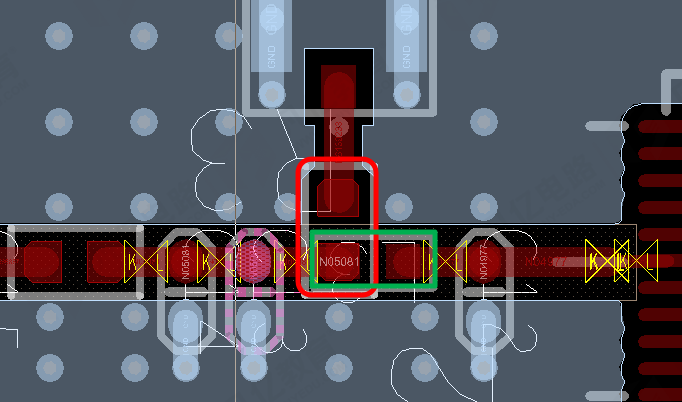

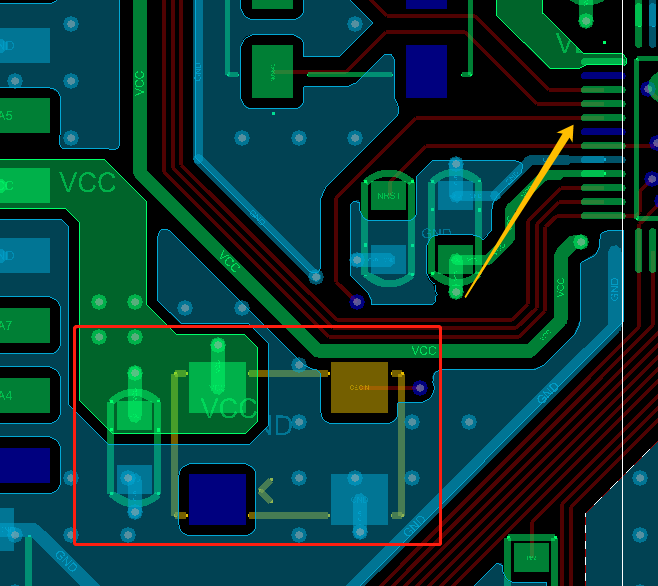

1.器件重叠,焊盘重叠会导致器件无法焊接。2.底层没有铺铜处理3.过孔应打到走线最后一段,完全包围走线。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.t

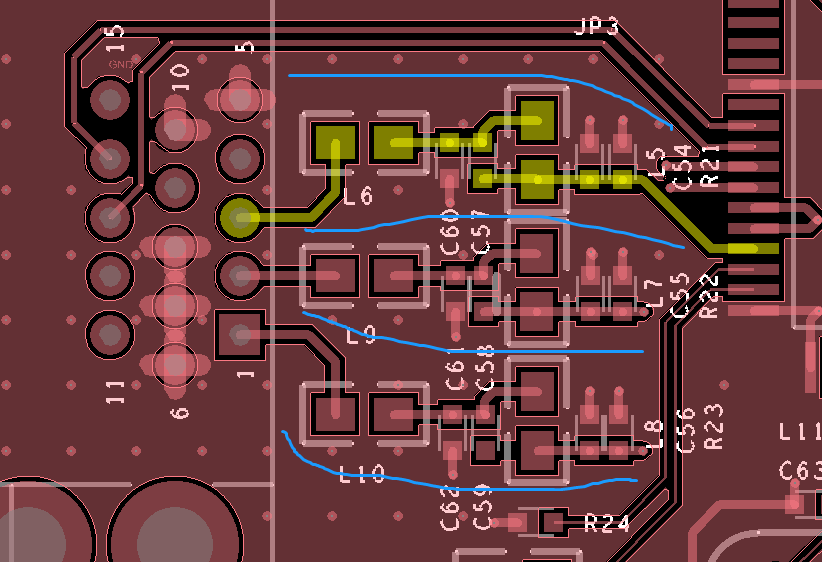

模拟信号需要一字型布局,单根包地处理2.晶振需要走内差分处理3.跨接器件旁边尽量多打地过孔,间距最少1mm,有器件不满足可以忽略,其他地方要尽量满足4.差分走线要尽量耦合5.百兆出差分信号外,其他信号都需要加粗到20mil6.模拟信号需要一

在电子设计领域,Pads和Allegro是电子工程师常用的两种EDA软件,有时候,工程师在面对项目设计时需要将Pads格式的文件转换为Allegro格式,以便与其他团队或供应商进行协作工作,所以本文将介绍一种方法,教你将将Pads文件转为A

在EDA工具里,Mentor Pads和Cadence Allegro是电子工程师常用的软件,在进行PCB设计时,经常会和其他人共同参与项目,如果遇见了将Allegro电路板文件转换为Pads文件格式该如何做?这篇文或许能帮上你!1、准备工

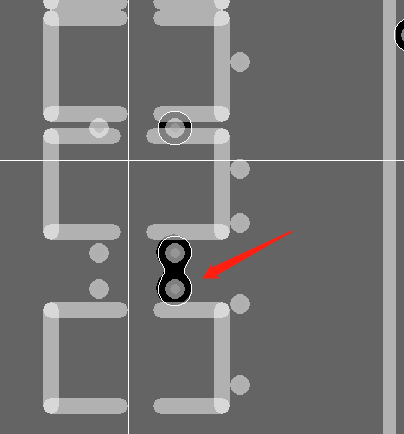

一直以来很多工程师都想进入中国大厂里工作,而Allegro作为中国大厂使用率最高的EDA软件,更是这些工程师的重点学习软件,但在学习过程中遇见器件被锁定,通过多种方法仍然无法解决,该怎么办?1、检查设计规则和限制检查设计规则和限制文件,确保

注意过孔间距,不要造成平面铜皮割裂:注意地址控制时钟组跟数据组可以用GND走线间隔开:下面的数据一致用GND走线隔开:其他的走线等长没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

晶振靠近管脚放置,尽量少打孔换层,包地处理2.差分包地地线上需要多打地过孔3.器件摆放尽量对齐处理4.注意过孔不要上焊盘后期自己检查一下过孔上焊盘和过孔重叠5.信号包地应该用地网络,不要用电源6.SD卡组内误差不能超过400mil7.注意走

很多电子工程师在进行项目时,经常会被要求减少预算或降低成本,以此提高企业竞争力、增加利润并满足市场需求,面对这些要求,电子工程师如何实现最大化?1、技术方面①选择合适的设计工具尽量采用主流PCB设计工具,如AD、Allegro等,可提高设计

随着电子设计领域的不断发展,Allegro工程师的需求也越来越高,在发展过程中,不同等级的Allegro工程师之间存在着薪资和工作范围上的差异,那么你知道不同等级的Allegro工程师有什么不同吗?1、初级Allegro工程师①分布情况初级

在PCB设计中,电子工程师可能会需要将一个已经设计好的PCB复制到另一个PCB中,以此减少重新布局和连接的工作量,在Cadence Allegro软件中如何实现这一步骤?这篇文或许能给你些参考。1、打开原石PCB和目标PCB文件首先,打开包

扫码关注

扫码关注