- 全部

- 默认排序

答:这样的情况是非常少见的,原理图所添加的网络名称非常长,导致不能导入到PCB文件中,我们这里讲解一下如何设置,原理图中跟PCB文件中都需要设置,具体操作如下所示:

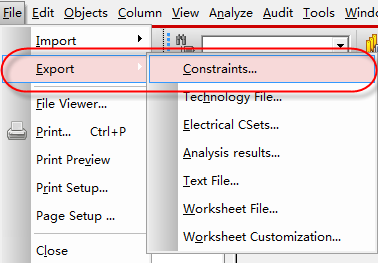

答:我们使用ALLEGRO软件进行PCB设计,其中的PCB布局布线都可以进行复用,那么它所设置的规则,比如物理规则、间距规则,是否也可以进行复用呢,当然是可以的,具体复用操作的步骤如下所示:第一步,打开已经设置好规则的PCB文件,执行菜单命令Setup-Constraints,在其下拉菜单中选择Constraint Manager,进入到规则管理器中;

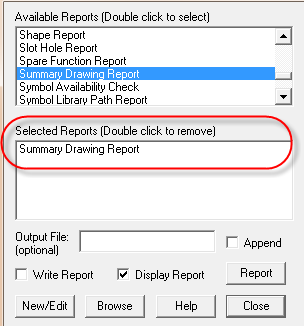

答:我们在进行PCB设计时或者PCB设计完成以后,作为设计工程师都希望把控整个PCB文件的总体信息,这里我们讲解一下如何去查看PCB设计文件的总体信息报告,具体如下所示:

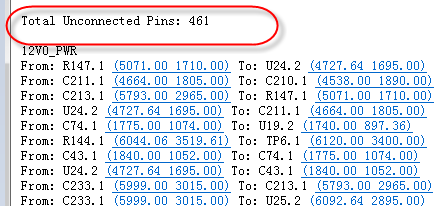

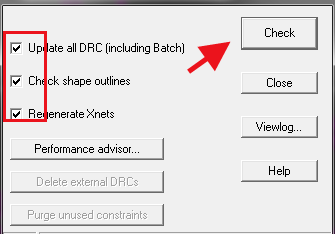

答:我们在进行布线的过程中,为了加快布线的效率,我们应该如何快速的定位PCB中哪些管脚是没有连接的呢,具体的操作步骤如下:

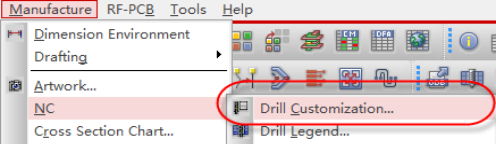

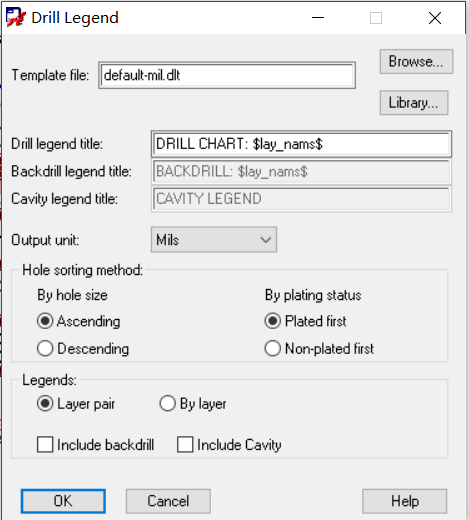

答:当PCB设计完成以后,需要输出相关的光绘文件,在这之前,我们需要提取钻孔的信息,我们这里讲解一下,如何去查看PCB文件上的钻孔文件信息,具体操作如下所示:

答:在第492问中,我们讲解了如何去查看PCB文件的钻孔信息,我们需要将这些信息输出,并提取钻孔符号的表格,具体操作步骤如下所示:

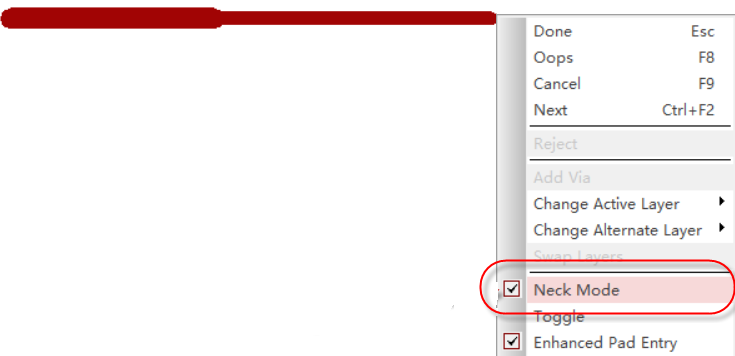

答:这里所说的瓶颈模式,指的就是在某些特定的区域,按照阻抗线宽去进行走线,线走不出来,需要更小的线宽,这时候就可以采用瓶颈模式去进行走线,具体的操作步骤如下所示:

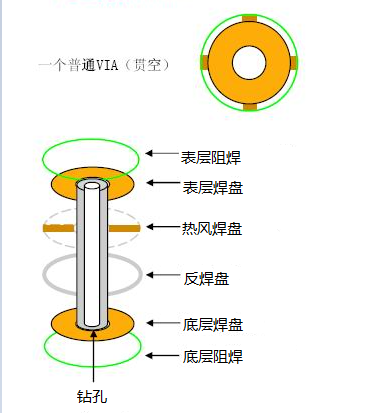

答:过孔,也叫金属化孔。在双面板和多层板中,为连通各层之间的印制导线,在各层需要连通的导线的交汇处钻上一个公共孔,即过孔。

ALLEGRO在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种:当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单栏命令“To

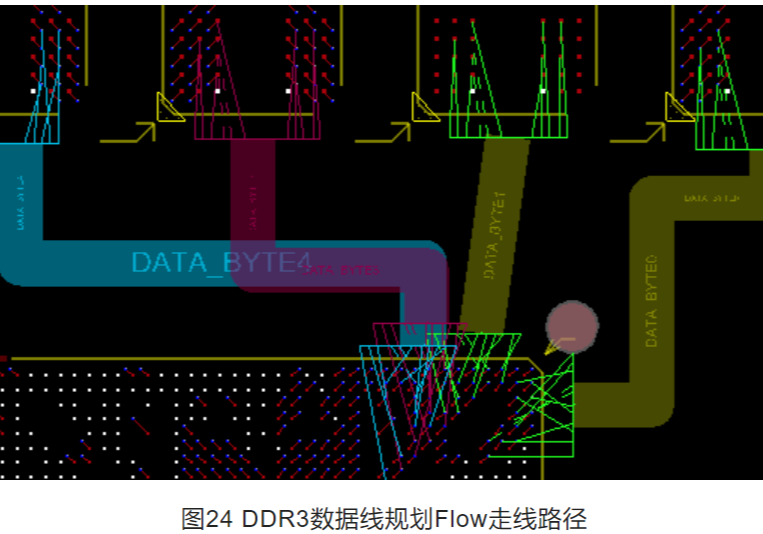

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

扫码关注

扫码关注