- 全部

- 默认排序

答:添加完成走线的阻抗线宽之后,这样PCB板上信号走线就会按照所设置的物理走线线宽进行。除了添加走线的线宽之外,还需要添加间距规则,来规范不同元素之间的间距,满足生产的需求,添加间距的操作步骤如下所示:

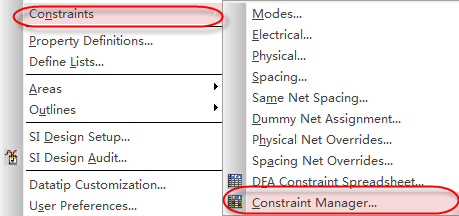

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

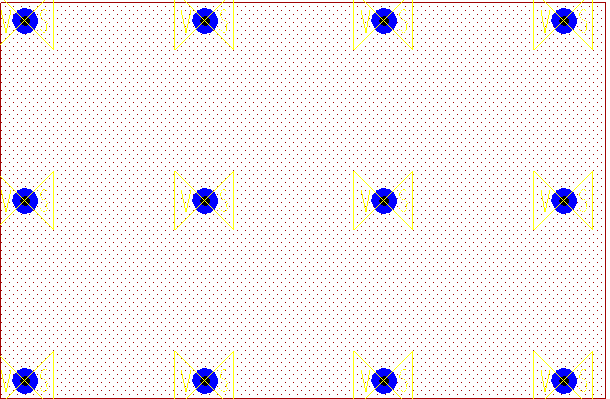

答:我们在ALLEGRO软件中,铺铜的时候,有两种铜皮可以选择,一种是静态铜皮,一种是动态铜皮,如图6-101所示,是静态铜皮,如图6-102所示,是动态铜皮。

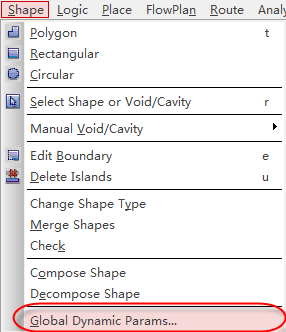

答:我们在ALLEGRO软件中,我们在铺铜的时候,需要事先对铜皮与焊盘的连接方式进行设置,有全连接、十字连接等多种连接方式,我们需要对全局的铜皮的连接方式进行一个设置,具体的操作步骤如下所示:

答:我们在进行设计的时候,如果是在同一层进行铺铜处理,当出现有两个或者两个以上的铜皮重叠的情况出现,如图6-106所示,A铜皮与B铜皮重叠在一起,A铜皮的优先级要高于B铜皮,所以A铜皮是保持原来的形状的,B铜皮会自动避让一块。

答:平面分割设计,是PCB设计中一项非常重要的事项,我们在处理完PCB的走线以后,会 处理电源还有地,地平面一般是完整的,一般不需要分割,电源平面一般会分割几个电流比较大电源,我们这里讲述一下如何对电源平面进行分割,具体操作如下:

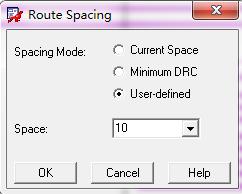

答:我们在进行PCB布线的时候,当遇到一把一把的总线的时候,如果是一根一根线的去走,是很费时间的,所以呢,这里我们讲解一下,在ALLEGRO中如何去进行多根走线以及在走线的过程中如何对一组线的间距进行设置,具体的操作步骤如下所示:

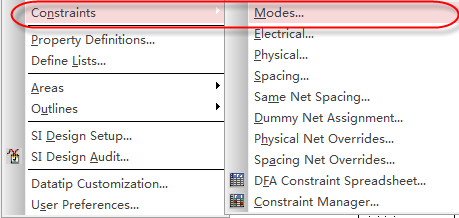

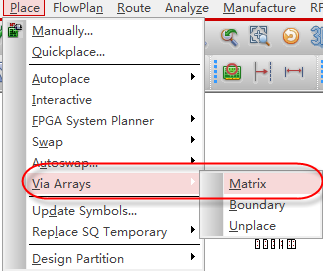

答:所谓的阵列过孔,就是在某一个区域或者走线上,按照某种特定的规律,均匀整齐的放置过孔,执行菜单命令Place-Via Arrays,进行阵列过孔的放置,如图6-121所示,在下拉菜单中有三个选项,具体的含义如下:

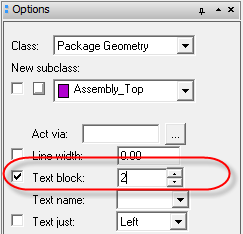

答:我们在进行元器件参考编号调整之前,首先需要对PCB中所有的元器件的参考编号进行大小的统一,方便后期PCB进行生产,印刷出来统一整齐,这里讲解一下,如何对PCB中的元器件编号进行统一的大小调整,操作如下所示:

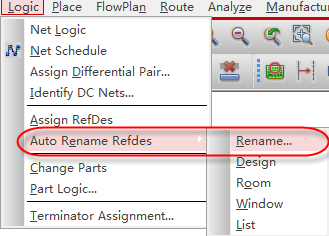

答:当PCB设计完成之后呢,在调整元器件的参考编号时候,会发现元器件的参考编号非常乱,原理图在设计时没有进行统一的编号处理,为了管理方便,可以在PCB中对元器件的参考编号进行重新排列,具体操作如下所示:

扫码关注

扫码关注