- 全部

- 默认排序

Altium Designer在国外发布了正式版本,AD在国内也宣布AD正式版正式发布了,并且AD的官网也提供了AD正式版的下载试用,版本Altium_Designer 改进更快效果更佳的自动交互式布线技术,这个特性从AD引入,现在在算法上效率得到了极大的提升。

Altium Designer在国外发布了正式版本,AD在国内也宣布AD正式版正式发布了,并且AD的官网也提供了AD正式版的下载试用,版本Altium_Designer 改进更快效果更佳的自动交互式布线技术,这个特性从AD引入,现在在算法上效率得到了极大的提升。

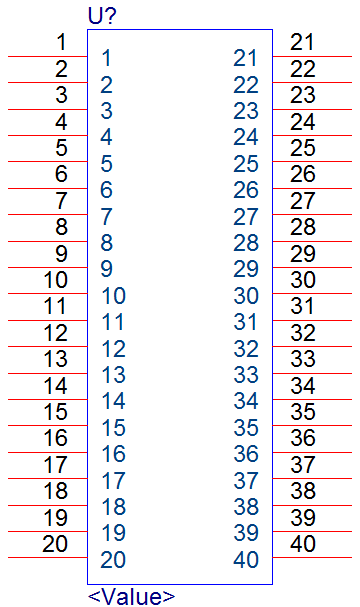

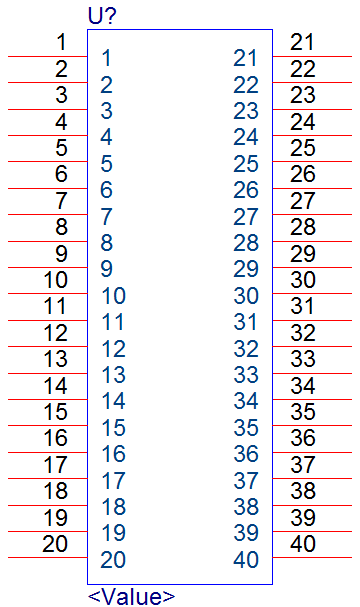

针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改,操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称Name以及管脚编号Numbers先按数字1、2、3...,一致往下排,如图2-64所示; 图2-64编辑管脚属性示意图第二步,用鼠标左键框选所有的管脚,点击右键,Edit Properties…,编辑属性,如图2-64所示;第三步,在弹出的界面中进行对应参数的设置即可,如图2-65所示,可以运用对

Altium Designer 20.1.14 Build 287 Win64最新版百度网盘安装包下载,Altium Designer在国外发布了正式版本,AD在国内也宣布AD正式版正式发布了,并且AD的官网也提供了AD正式版的下载试用,20版本Altium Designer 改进更快效果更佳的自动交互式布线技术,这个特性从AD引入,现在在算法上效率得到了极大的提升。

7月20日,美贸易代表办公室(USTR)公布了针对中国商品加征关税的累计第32批排除清单,主要涉及3000亿关税产品List 4A清单中51个税号下64个品项商品,其中11个税号下的商品完全排除;包含部分纺织品、部分塑料制品、锂离子电池、运动头盔、健身器材、镀锌钢配件、婴儿床上用品、无线通信设备、收藏品等产品。即本次排除清单中的64个品项产品,自加征实施之日(2019年9月1日)起至2020年9月1日免加征7.5%的关税。

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

答:针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改,操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称Name以及管脚编号Numbers先按数字1、2、3...,一致往下排,如图2-64所示; 图2-64编辑管脚属性示意图第二步,用鼠标左键框选所有的管脚,点击右键,Edit Properties…,编辑属性,如图2-64所示;第三步,在弹出的界面中进行对应参数的设置即可,如图2-65所示,可以运

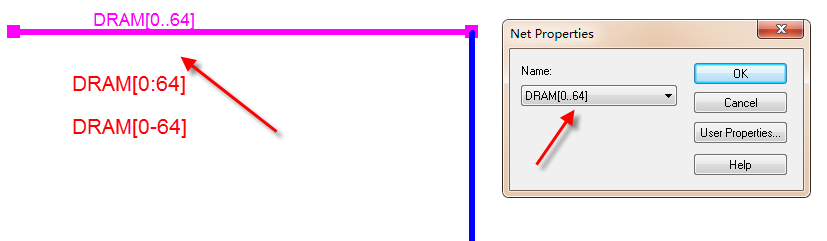

答:在前面的问答中,我们已经创建好总线了,创建好总线以后,我们需要在总线上放置好总线的名称,也就是网络标号,按照网络一一对应,总线的命名方式分为三种,如下列:Busname[0..64],其中Busname是总线名称,0到64是总线中包含的分支数目;Busname[0 :64],其中Busname是总线名称,0到64是总线中包含的分支数目;Busname[0-64],其中Busname是总线名称,0到64是总线中包含的分支数目。我们在命名总线的时候,放置的是网络标号Net Alias,点击菜单P

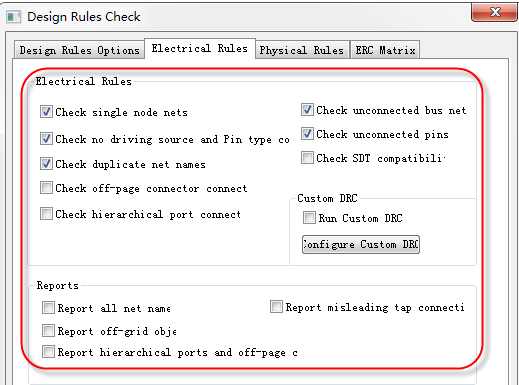

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

扫码关注

扫码关注