- 全部

- 默认排序

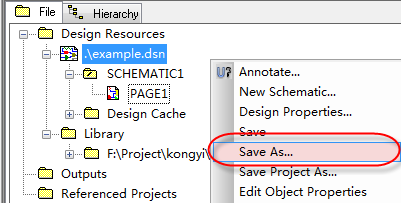

答:我们在进行原理图设计或者是进行PCB设计,都会遇到这样的问题,需要降低设计文件的版本,我们这里讲解下,Orcad软件设计的原理图如何去降低原理图的版本,操作的步骤很简单,我们这里列举一下操作的步骤:第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本; 图3-212 原理图另存低版本示意图第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的

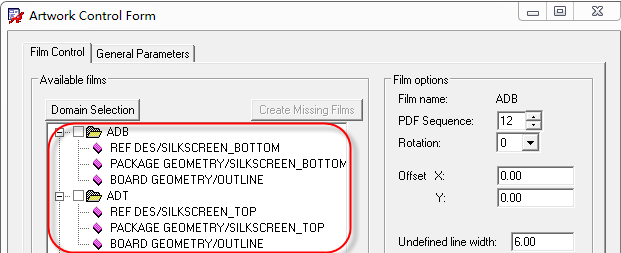

答:第一步,需要设置装配的光绘层叠,点击执行菜单命令Manufacture-Artwork,进行光绘层叠的设置,进入光绘层叠设置界面,添加顶底两层的信息即可,如图5-213所示:

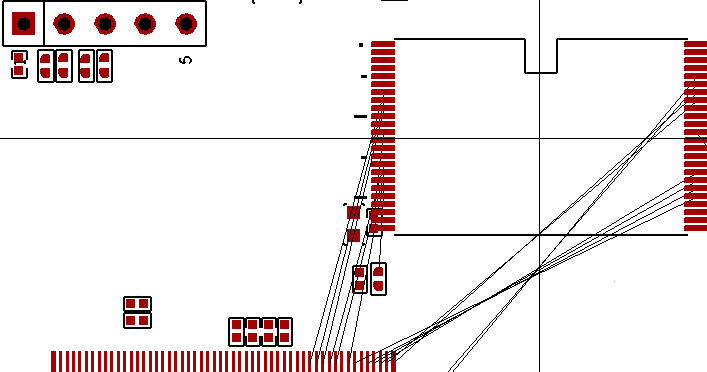

答:我们在进行布局的时候,执行移动命令,移动的时候会显示器件的飞线,方便引导工程师进行布局,如图6-213所示,移动哪个器件,哪个器件就会显示飞线。

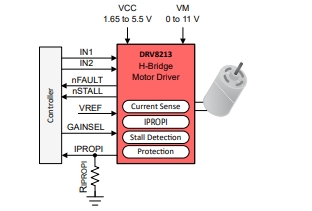

1、DRV8353RHRGZR三相智能栅极驱动器48VQFNDRV835x 系列器件均为高度集成的栅极驱动器,适用于三相无刷直流 (BLDC) 电机 应用标准。这些 应用 包括 BLDC 电机的场定向控制 (FOC)、正弦电流控制和梯形电流

开发板使用LPC2136芯片,晶振采用14.7456MHz的,后来改成10.0000MHz就出错了, 使用14.7456MHz时参数如下: #define Fosc 14745600 #define Fcclk (Fosc * 3) #define Fcco (Fcc

扫码关注

扫码关注