- 全部

- 默认排序

答:在做PCB设计过程中,叠层时可以选择是负片工艺还是正片工艺,如果层数较少,一般都可以正片处理,层数较多、数据量较大时会选择负片工艺对电源层进行处理。

自述:本人供职于某物联网公司,在其做硬件工程师已长达五年了,五年的光阴让我混圆了肚子,混秃了额前的青丝,作为一名资深的“裱糊匠”,每天烦恼的,并不是搭建这个那个系统,也并不是画原理图,而是各种的打交道,外有客户的各种需求变更,内有PM的schedule压缩,CE的各种验证,采购的傲慢,layout的抱怨。。。

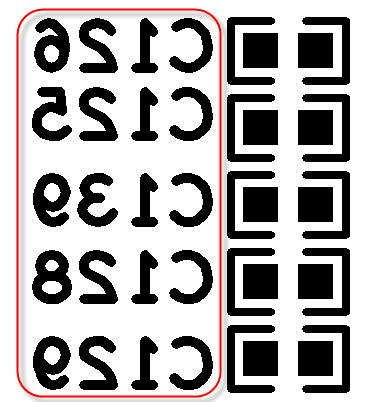

答:Allegro软件对于BOTTOM层的器件,其位号字符一般是镜像显示的,如图6-225示:

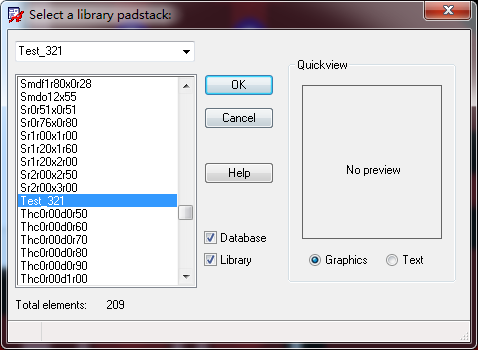

答:ICT (In Circuit Tester,自动在线测试仪)是印制电路板生产中重要的测试设备:用于焊接后快速测试元器件的焊接质量,能迅速定位焊接不良的引脚,以便及时进行补焊。体现在PCB设计上,则需要在设计中添加用于ICT测试的焊盘,并对符合测试点要求的焊盘添加测试点属性。因测试点焊盘和间距及位置有严格的要求,对于有ICT设计要求的板卡,建议在设计前就明确添加ICT的网络,拟定ICT的添加计划,在设计的过程中边布线边添加。如果在设计完后再添加ICT测试点,必将大量返工,甚至有的网络根本无法

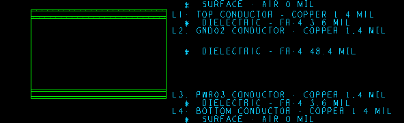

答:在生成的Gerber中,除了要将PCB上的走线、过孔等内容包含进去,还需要将PCB的叠层等信息制作进去,以便提供详细的文件给工厂生产,Allegro提供了一个直接提取设计参数生成的叠层表格的功能,减少了设计者的工作量。

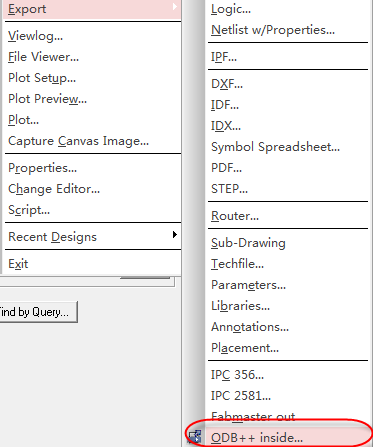

答:ODB++是业内产常用的一种规范的生产文件,该格式文件所包含的信息较常规RS274X格式的光绘文件丰富许多。而常规的Allegro软件并不能实现该功能,安装ODB++组件方可实现,Cadence网站有提供下载。

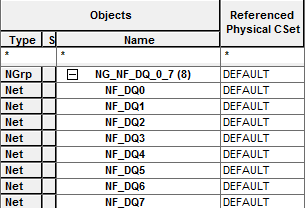

答:在16.6及以上的版本中已经没有Bus总线了,如果需要添加的话,需要添加Net Group,可实现的功能和Bus总线是一样的。

答:首先,点击Setup-Design Parameter Editor命令,在Display选项卡中,勾选Via Lables选项,点击OK退出,如图6-254所示;

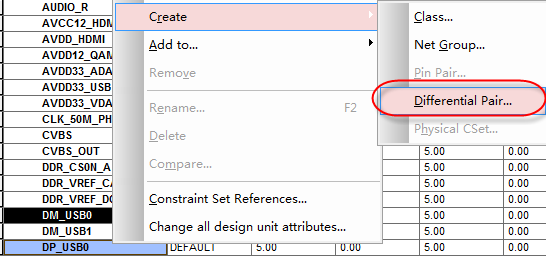

答:设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加。

扫码关注

扫码关注