- 全部

- 默认排序

电路进行验证,就只能通过ADS这类的工具来进行仿真验证和评估,如果知道芯片的类型并且有模型,可以针对性的进行特定的仿真,如果不知道芯片的型号或者没有模型,就使用ADS中的TX_Diff和Rx_Diff元件,在元件可以设定信号的速率、PRBS的码型、抖动、均衡等参数,然后进行仿真评估;对于一些小公司而言,这就只能凭经验了。 在获得了连接器、线缆或者PCB背板的测试或者仿真S参数之后,可以在ADS中非常方便的判断是否满足总线或者设计的要求: 本文就和大家分享下在ADS中如何对这类的情况进行仿真分

此文从射频界面、小的期望信号、大的干扰信号、相邻频道的干扰信号以下几点解读射频电路四大基础性特性,并提供了在电路设计过程中都要非常注意的主要关键因素。 射频电路设计之射频的界面 无线发射器和接收器在基本概念上,可分成基频与射频两个部分。基频包含发射器的输入信号之频率范围之内,也包含接收器的输出信号之频率范围之内。基频的频宽影响了数据在系统中可流动的基本速率。基频是用于改善数据流的稳定度,并在特定的数据传输率之下,减少发射器产生在传输媒介的负荷量。 所以,电路设计基频电路时,都要更多的信号处

仅看近30年的发展,以PC为代表的行业几度繁荣而后归于平静,从最早的百兆级处理器速度倍频直到今天的几个GHz级别,总线位宽从16位扩展到今天的64位,以Intel为首的行业龙头公司将CPU的处理能力整整提升了成百上千倍。 在总线宽度和处理器速度达到瓶颈后的近10年里,整个行业将突破的战场放在了高速接口上,外部串行高速接口的速率从Gbps迅速飞升到几十个Gbps,为了实现更高的吞吐量,还采用了复杂的高阶调制和增加链路宽度的办法。这一切简直是以“迅雷不及掩耳盗铃之势”汹涌而至,作为“攻城狮”的你做

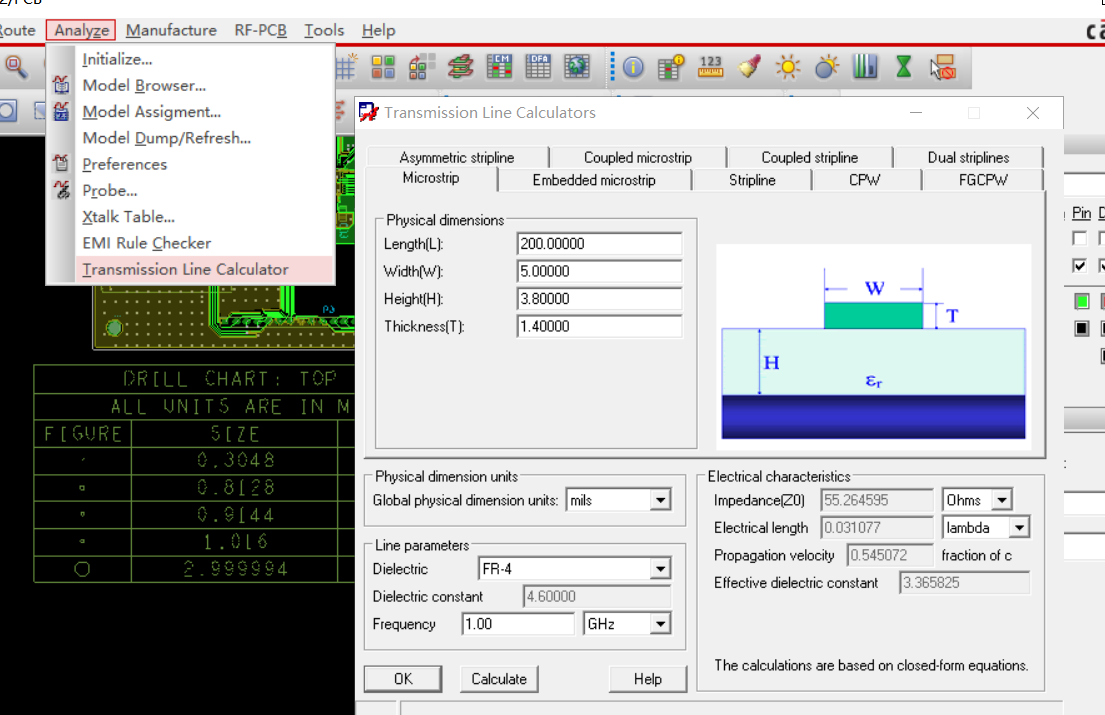

随着信号速率越来越高,PCB设计时,越来越多的数字电路 需要对走线阻抗控制、延迟等传输参数进行计算。Allegro16.6版本提供了一个内置的传输线参数计算工具,能对微带线、嵌入式微带线、带状线、差分线等多种传输数据结构进行传输参数计算。

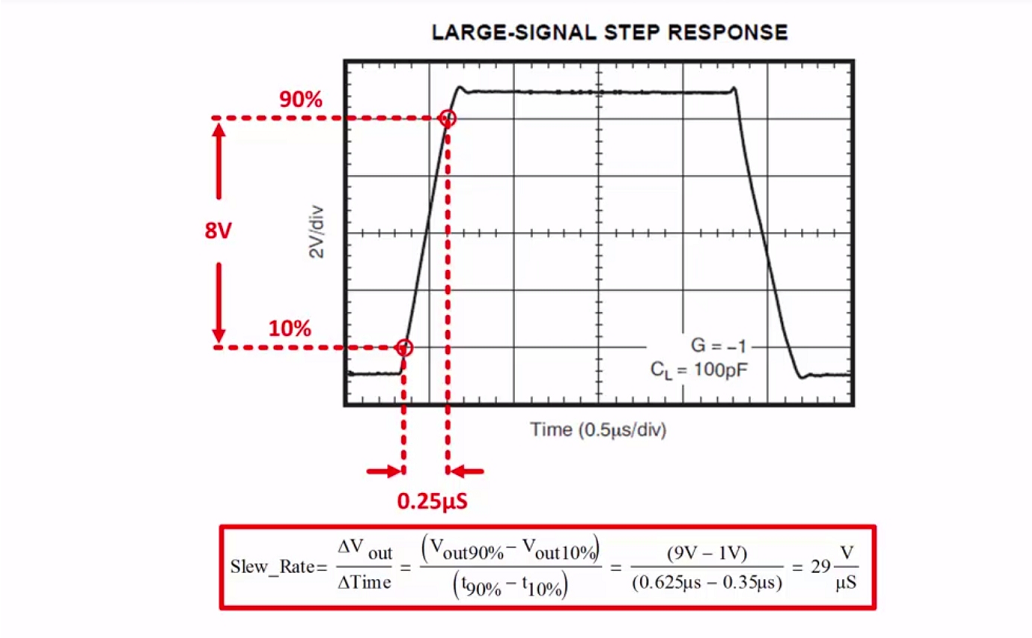

运放的压摆率

压摆率定义为运放输出电压可以达到的最大摆动速率,它以伏每微妙为单位,测量压摆率的时候可以在输入端放置一个较大的阶越信号,比如1V的伏值,然后测量输出端的电压摆动,也就是图中输出量从10到90的时间间隔,我们可以看下我们的这个0.25us,有些对应的数据手册中会对应给出压摆率的对应的指标,有些会用大信号的阶越信号来代替

研究人员新技术显著提升了锂离子电池用钛铌氧化物的性能-TNOx的氧空位和HRGO的高导电性,可以有效提高TNOx/HRGO混合物的电子导电性,而HRGO的空位有利于传输锂离子。在以上特性的协同作用下,TNOx/HRGO混合物的速率性能得到提高。

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

曾经,业界发起过一个话题“Sub6+毫米波才是真5G”,引发了很多技术大牛探讨,5G毫米波的性能非常强大,很适合应用在万物互联时代,非视距速率可达200+Mbps,视距速率高达1+Gbps,最高性能可达LTE的10倍。然而很多人不太清楚5G

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注