- 全部

- 默认排序

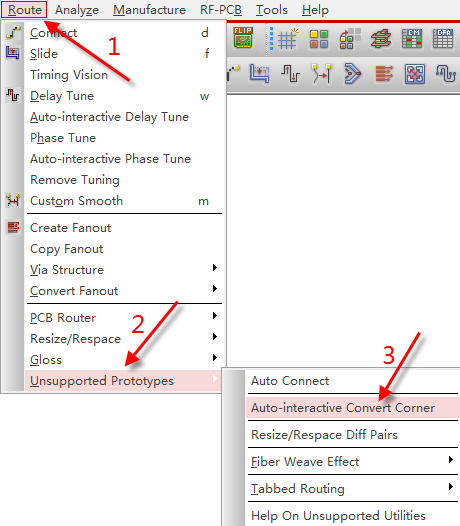

答:一般我们在处理PCB走线的时候,都是45度走线,当遇到比较高速的信号时,为了满足阻抗的一致性,可以设置成为圆弧走线,在16.6版本以后,可以对45度的走线自动转换为圆弧的功能,具体操作如下:

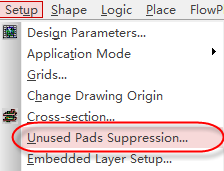

答:做无盘设计的目的,是因为通孔的焊盘在内电层,是具有寄生电容的效应的,容易造成阻抗的不连续,导致信号出现发射,从而影响信号的完整性,所以在处理高速信号时候,在PCB设计端就将走线连接层的焊盘去掉,最大程度的保持地过孔与通孔连接处的走线阻抗一致,具体操作的步骤如下所示:

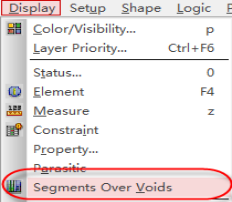

答:我们在PCB中进行布线的时候,高速信号先都是需要做阻抗设计的,做阻抗设计必须要有完整的参考平面,为了保证阻抗的连续性,高速信号尽量不要跨分割,所以我们在设计过程中都需要进行检查,具体操作步骤如下所示:

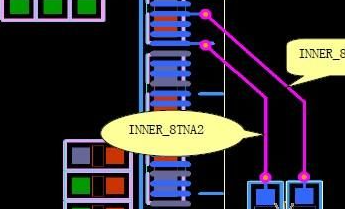

答:我们在进行差分布线设计的时候,特别是高速信号差分,在进行打孔换层的时候,都会在旁边添加回流地过孔,若差分信号比较多的时候,去添加,就非常繁琐,也容易遗漏,我么这里讲解一下,如何去进行自动添加,具体操作如下所示:

答:高速电路设计中电容的作用有如下几个:电荷缓冲池。电容的本质是储存电荷与释放电荷,当外界环境变化时,使得驱动器件的工作电压增加或者减少时,电容可以通过积累或者释放电荷来吸收这种变化,即将器件工作电压的变化转变为电容中电荷的变化,从而保持器件工作电压的稳定;

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

华为OD招聘现需硬件工程师2名:岗位要求如下:1.电子、通讯相关专业本科或以上毕业;2.三年以上硬件研发工作经验,具有高速数字电路硬件设计优先;

扫码关注

扫码关注