- 全部

- 默认排序

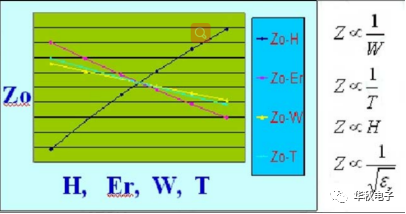

随着高速信号传输,对高速PCB设计提出了更高的要求,阻抗控制是高速PCB设计常规设计,PCB加工十几道工序会存在加工误差,当前常规板厂阻抗控制都是在10%的误差。理论上,这个数值是越小越好,为什么是10%?为什么不能进一步的把常规控制能力推到8%,甚至5%呢?从设计上,由理论公式推导,阻抗与介质厚度

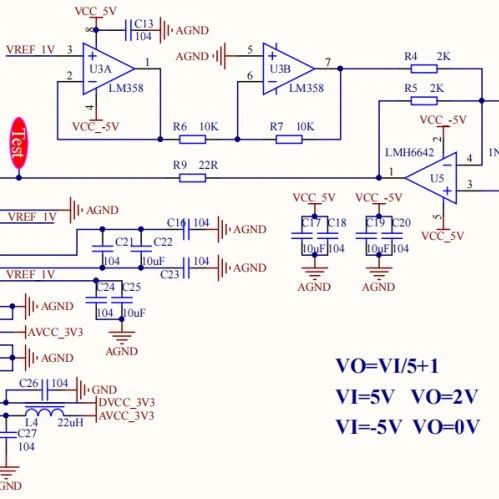

AD9280 在时钟(CLK)的驱动下工作,用于控制所有内部转换的周期;AD9280 内置片内采样保持放大器(SHA),同时采用多级差分流水线架构,保证了 32MSPS 的数据转换速率下全温度范围内无失码;AD9280 内部集成了可编程的基准源,根据系统需要也可以选择外部高精度基准满足系统的要求。A

购买的4片DDR3 T点拓扑高速pcb设计速成实战视频中没有支路的等长视频,视频中只是说书有讲,但是书上讲的不是很详细,支路的等长我还是不太会吖,能否录个支路的等长视频给我,能否录个from to的用法视频

购买的4片DDR3 T点拓扑高速pcb设计速成实战视频中没有支路的等长视频,视频中只是说书有讲,但是书上讲的不是很详细,支路的等长我还是不太会吖,能否录个支路的等长视频给我,能否录个from to的用法视频

我有几个问题,想请教下。

我有几个问题,想请教下。fpga的,普通io是什么电平标准呢ecl.还是cml,lvds,那种标准。因为,实际高速设计时需要通过电平标准,来设计匹配电路但我没在手册上,看到过相关描述

老师,我画了个板子,spi已经等长处理了,但还是只能跑到10m,速度再高波形就有严重变形了。除了等长还需要怎样处理?

今天遇到了这个问题,领导让我改成135°线,说这样不行电路板好看很重要吗,没谁天天盯着电路板瞅吧他给我的回复不是好不好看是他觉得有问题刚我搜的因为我认为直接走线会比45更好因为我要辞职了,然后我回复他我说我记得之前培训(或者还是那个技术文章)任意走线会比45好一些,弯越多信号反射越大,所以我现在布线

扫码关注

扫码关注