- 全部

- 默认排序

随着高速信号传输,对高速PCB设计提出了更高的要求,阻抗控制是高速PCB设计常规设计,PCB加工十几道工序会存在加工误差,当前常规板厂阻抗控制都是在10%的误差。理论上,这个数值是越小越好,为什么是10%?为什么不能进一步的把常规控制能力推

阻抗是电子电路中电流和电压之间的相对关系,是电路元件对交流信号的阻碍程度,是电路元件对交流信号的阻碍程度,在电子电路设计中,准确计算和控制阻抗对于确保信号完整性,抑制噪声和实现高性能至关重要,所以下面将聊聊一些常见的阻抗计算公式,看看你有没

很多人在电子设计时经常会接触到接地阻抗和接地电阻这两个元件,由于这两类名字和功能相似,很多人会将其混为一谈,然而这种想法是错误的,下面将教你如何分清接地阻抗和接地电阻。1、接地阻抗接地阻抗值得是系统或电路板上接地节点的阻抗,是由接地系统的物

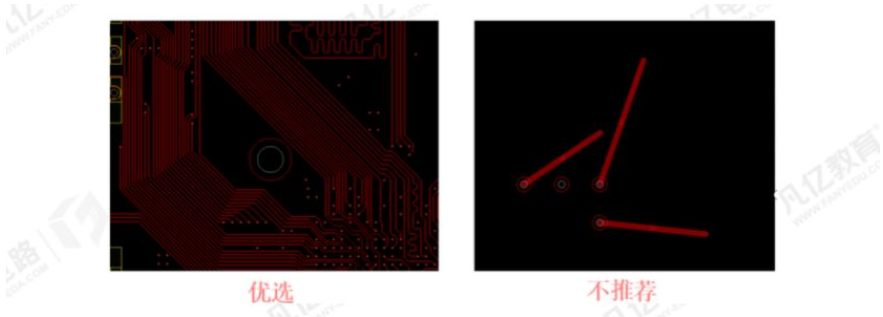

1、走线长度应包含过孔和封装焊盘的长度。2、布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。图1 PCB布线的角度3、布线避免直角或者锐角布线,导致转角位置线宽变化,阻抗变化,造成信号反射,如图2所示。图2 走线的锐角与

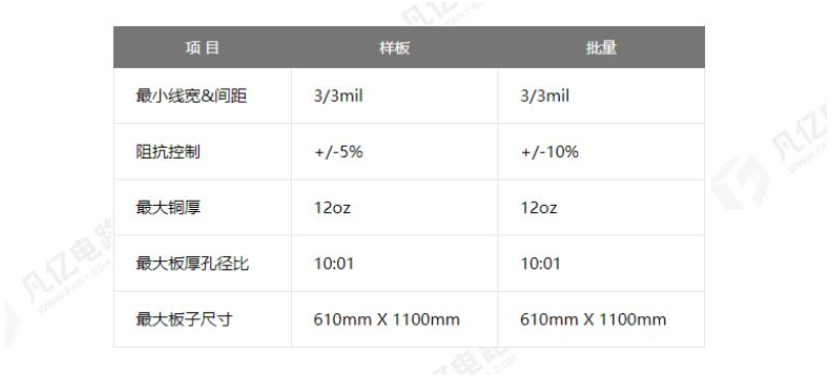

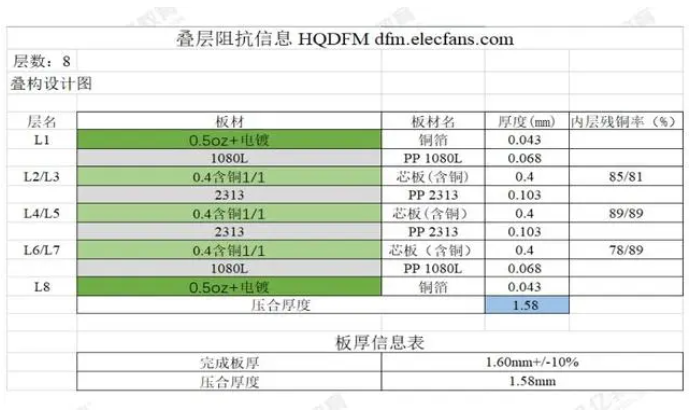

一、关于PCB布线线宽1、布线首先应满足工厂加工能力,首先向客户确认生产厂家,确认其生产能力,如图1所示。如客户无要求,线宽参考阻抗设计模板。图1 PCB板厂线宽要求2、阻抗模板,根据客户提供的板厚及层数要求,选择合适阻抗模型,布线线宽按阻

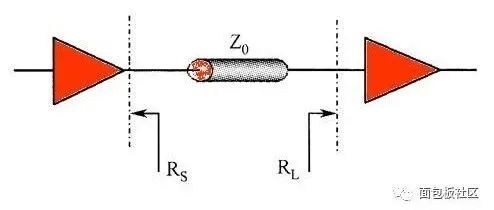

为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。由于最小线宽和最小线

为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。由于最小线宽和最小线

详解阻抗匹配原理

本文主要详解什么是阻抗匹配,首先介绍了输入及输出阻抗是什么,其次介绍了阻抗匹配的原理,最后阐述了阻抗匹配的应用领域,具体的跟随小编一起来了解一下吧。一、输入阻抗输入阻抗是指一个电路输入端的等效阻抗。在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin就是U/I。你可以把输入端想象成一个电

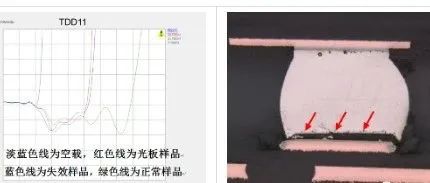

什么是TDR

1、TDR时域反射技术原理TDR (Time Domain Reflectometry)时域反射技术的原理是,信号在某一传输路径传输,当传输路径中发生阻抗变化时,一部分信号会被反射,另一部分信号会继续沿传输路径传输。TDR是通过测量反射波的电压幅度,从而计算出阻抗的变化;同时,只要测量出反射点到信号

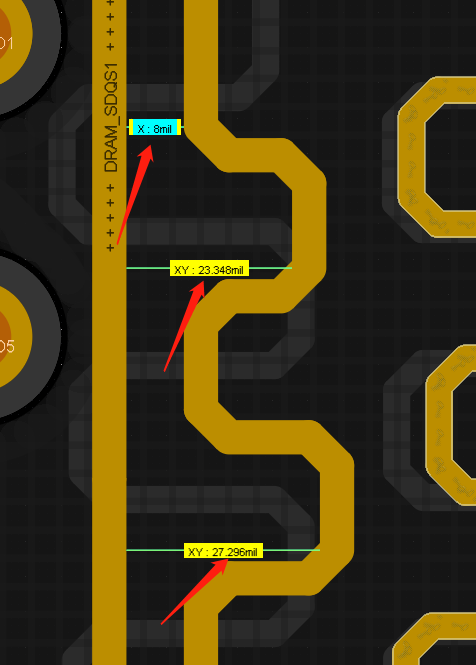

差分对内等长凸起高度不能超过线距的两倍2.注意T点的间距要求,后期自己看视频在了解一下3.地网络需要就近打孔,缩短回流路径4.VREF的电源最少要加粗到15mil以上5.此处不满足载流6.注意差分走线要尽量耦合,满足差分间距要求,控好阻抗7

扫码关注

扫码关注