- 全部

- 默认排序

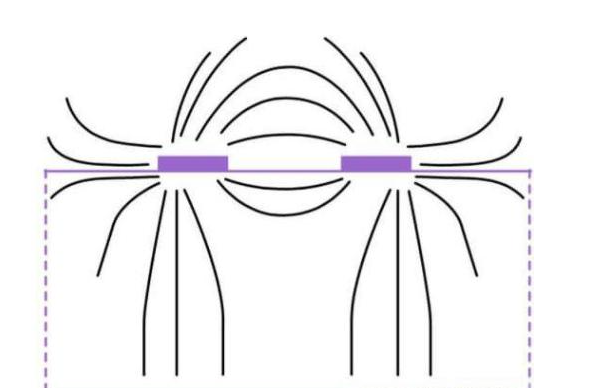

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

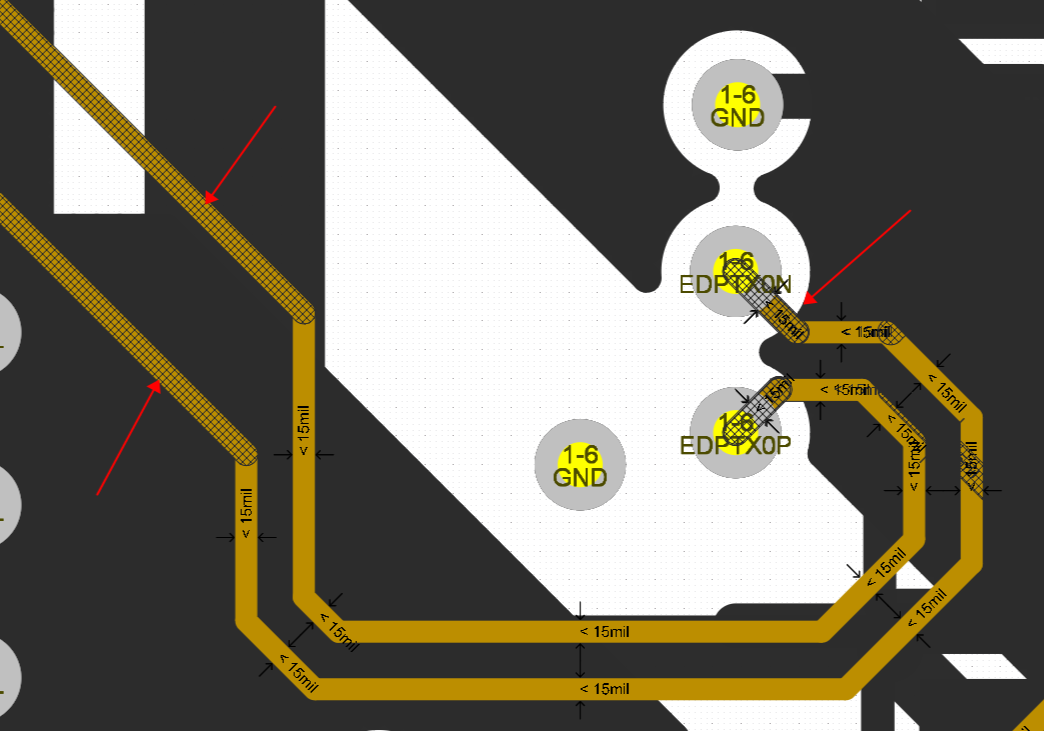

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

扫码关注

扫码关注