- 全部

- 默认排序

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

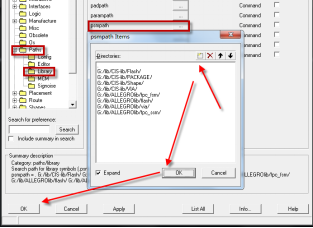

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

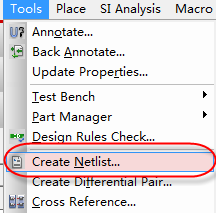

答:现在市面上用的最多的是,Orcad软件绘制原理图,Allegro软件绘制PCB版图。我们现在讲解一下怎么使用Orcad软件将绘制好的原理图,输出第一方的网表,然后将第一方的网表导入到Allegro软件中,具体操作如下:

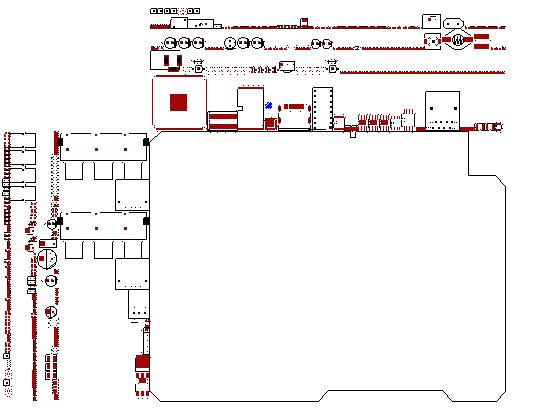

答:很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:

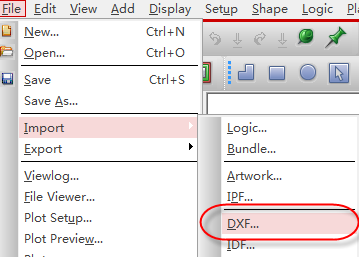

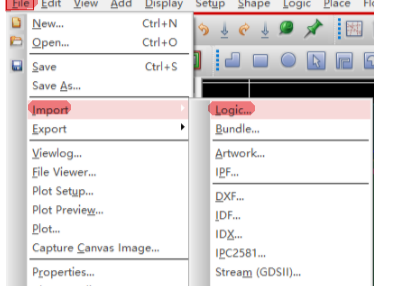

答:我们在进行PCB设计之前,除了将原理图的网表导入,将元器件放置在PCB板上,还需要做的就是将结构文件导入到PCB中,进行结构器件的定位。这里呢,我们详细讲解一下结构文件如何导入到PCB中,具体操作如下:

一个学习信号完整性仿真的layout工程师作为layout工程师,首先的输入条件就是原理图,也就是常说的(原理图导出网表文件)网表文件,有硬件工程师会直接把网表发给我们,有的直接给我们dsn文件,要求我们自己导出导入网表,下面简单介绍导出导

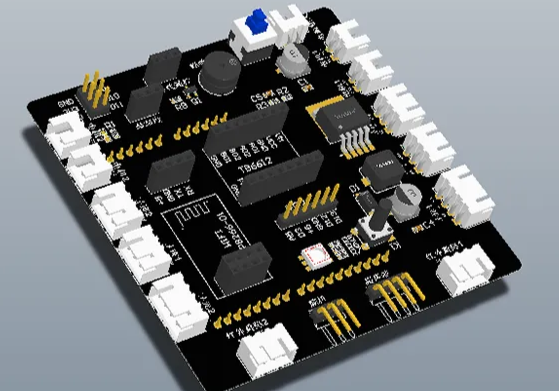

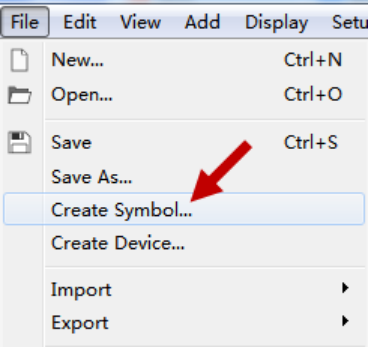

在设计时经常会碰到网表导入的情况,网表导入到PCB中时,第三方的网表需要指定事先指定好PCB封装库文件,并产生Device文件,才可以将网表导入到PCB中,第一方网表只需要psm文件跟pad文件,是不需要device文件的。1、 PCB封装

如何做好PCB设计的网表输入操作?网表输入操作是PCB设计前期的准备工作,而良好的网表输入能给PCB设计增上添花,间接提高设计效率,但很多电子小白更加重视PCB设计及加工,经常忽略网表输入,这是不正确的做法,我们来看看网表输入该如何做好?P

用Design Entry CIS生成逻辑网表的时候没有报错,能够成功的生成pxlBA.txt,netlist.log,pstchip.dat,pstxnet.dat,pstxprt.dat五个文件,这五个文件在同一个文件夹NetList下。然后一个叫work2的文件夹使用PCB Design GX

扫码关注

扫码关注