- 全部

- 默认排序

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

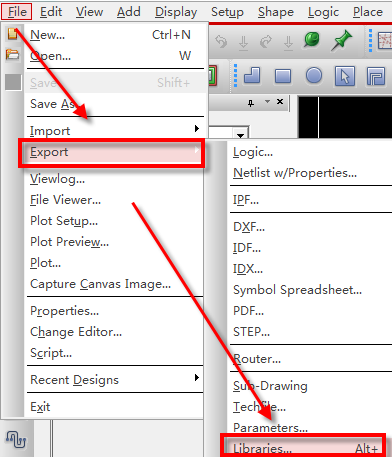

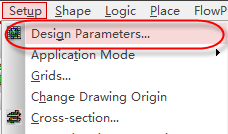

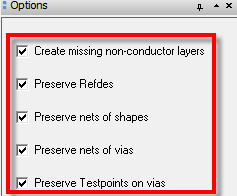

答:在导网表时,如果碰到有缺失Flash的报错,而正好缺失的Falsh在另一个项目中使用过,我们可以从另一个PCB中调用,具体的步骤如下:第一步,打开PCB,点击File-Export-Libraries…,在弹出的对话框中勾选Shape and flash symbols、No library dependencies选项,设置好导出的文件夹路径,点击Export导出,如图4-111所示;

答:在Allegro软件16.6版本及以上版本,新增加了显示网络名称的功能,方便进行布线设计,这里,讲解一下,如何将网络命令进行显示,具体的操作步骤如下所示:第一步,需要将Opengl模式开始,进入用户参数设置界面,在Display显示界面选择Opengl,右侧的第一项复选框不要勾上,如图5-169所示;

答:在做PCB设计时,如果需要对整个PCB板进行旋转,具体操作的步骤如下所示: 第一步,将PCB上所有元素进行解锁Unfix,然后点击Display-Color/Visibility选项,在弹出的对话框中点击Global Visibility:后面的On按键;

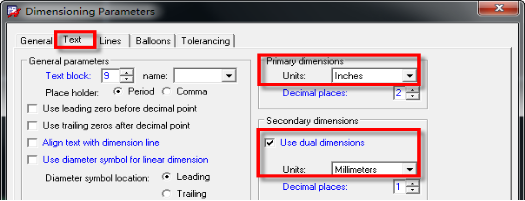

答:在PCB设计完成后,一般需要对PCB板框的长宽尺寸进行尺寸标注,标注时可以选择双单位显示标注的尺寸。第一步,点击Manufacture-Dimension Environment选项,然后右击选择Parameters选项;

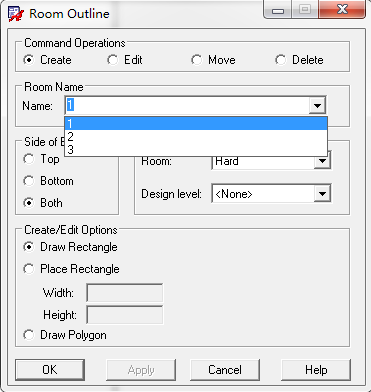

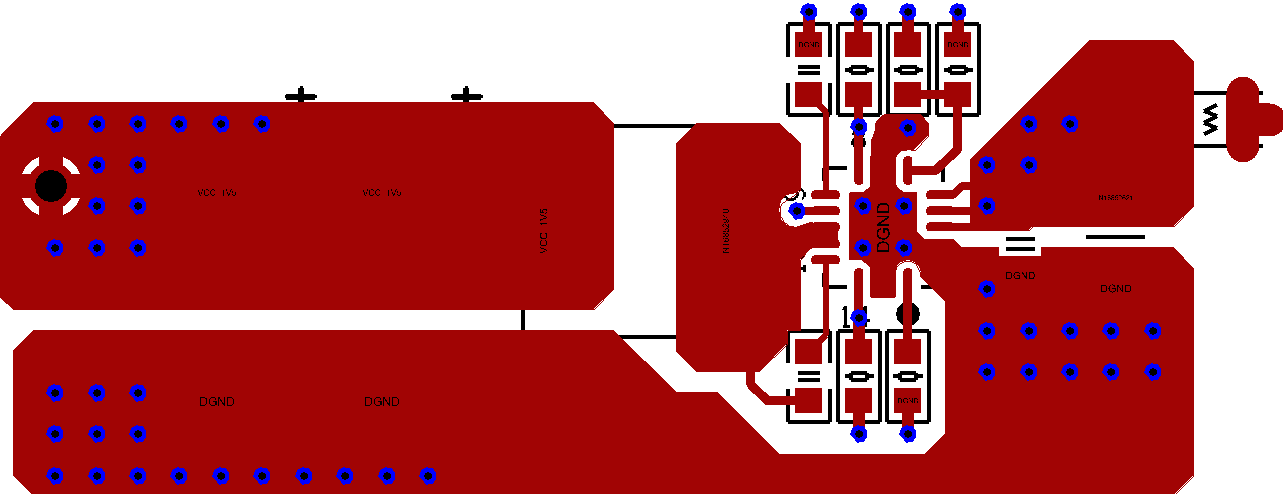

答:上述我们讲解了怎么快速的将元器件放置在PCB板上,通过图6-40所示的图可以看出,器件放置的都是很零散的,不是按模块或者是按页放置的,这里给大家介绍一些,通过在原理图添加ROOM属性,然后通过ROOM框在PCB板上来放置元器件,这样就可以根据模块或者一页原理图去发放置元器件了,具体操作如下:

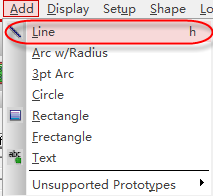

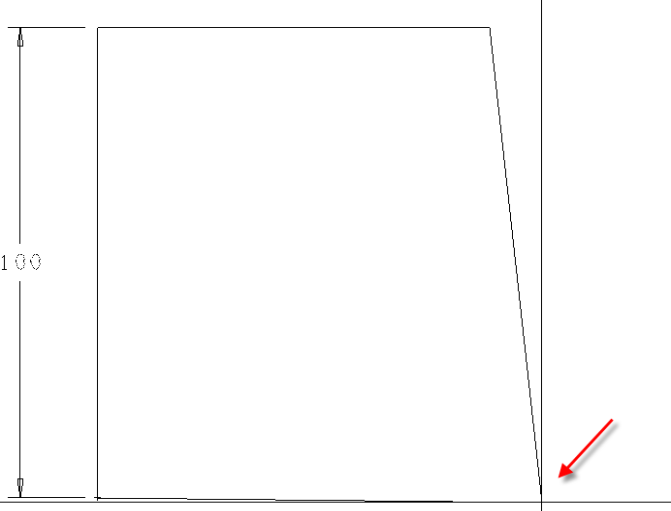

答:我们在绘制PCB时,所说的板框就是,整个PCB板子的外形,我们在设计之前需要将板框绘制好,设置好布局布线的区域,然后开始布局布线,这里我们讲解下,在Allegro软件中如何去绘制板框,以及一些绘制板框的方法与技巧,具体操作如下:

答:在上述的问答中,我们对所有的区域的含义进行了详细的描述,下面我们讲述下在PCB设计中对一些常用的布局布线区域进行设置,首先在绘制好板框的情况下,我们以Route Keepin为例,然后运用z-copy命令进行设置,具体的操作如下:

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

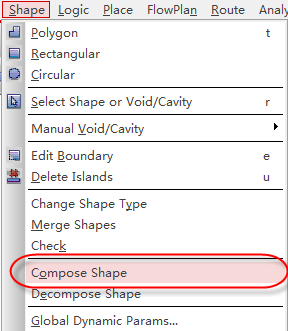

答:我们在进行PCB设计之前,都需要先绘制板框,在PCB绘制板框,都是绘制标准的,比如矩形、圆形,如果板框是异形的,一般是通过autocad软件绘制好之后,导入到PCB中。板框进行修改呢,也是如此,我们这里举例讲解一下,对于规则的板框绘制完成以后,我们应该如何对其进行修改,具体如下。

扫码关注

扫码关注