- 全部

- 默认排序

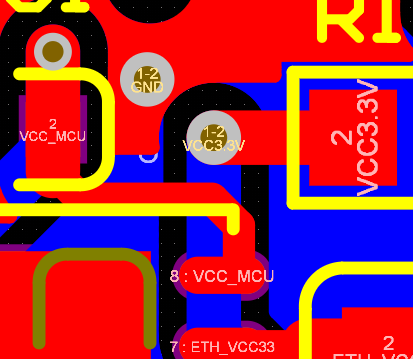

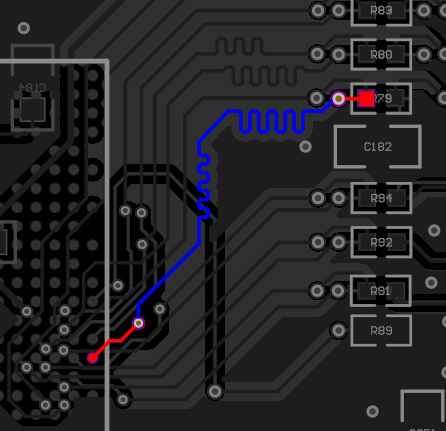

出线不要从管脚侧面出线差分对内误差控制在+-5mil以内时钟要包地处理散热焊盘背面要开窗处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.

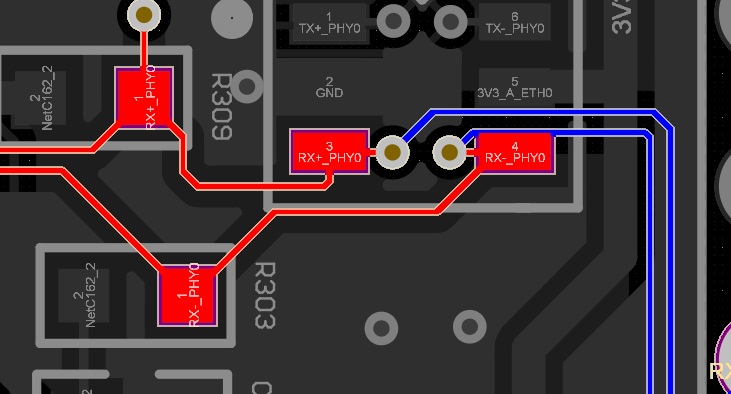

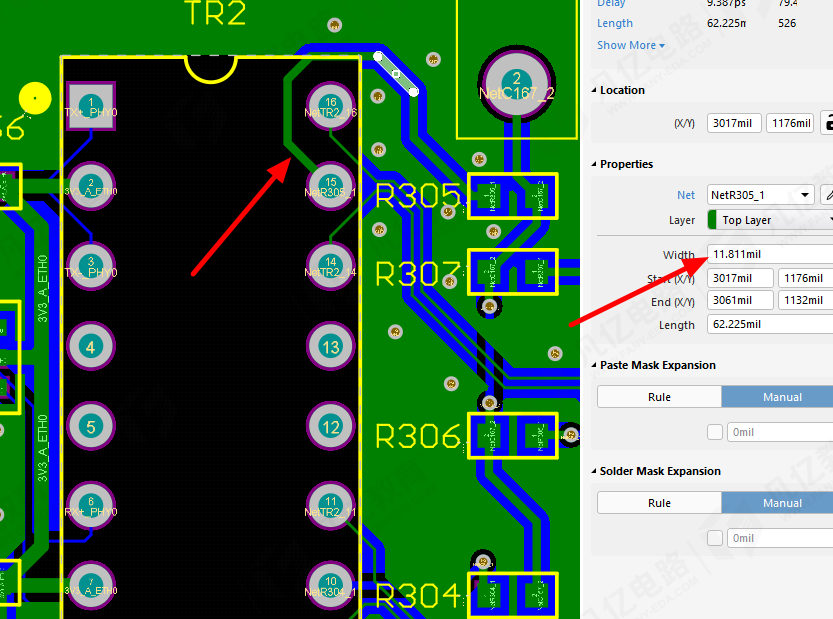

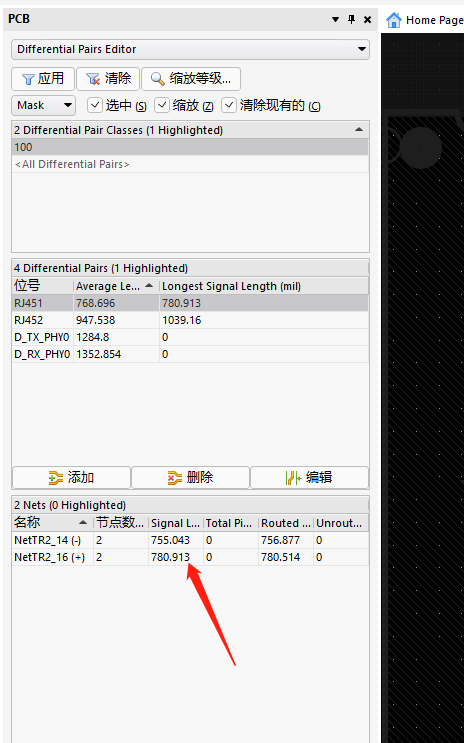

这里差分走线可以优化一下差分对内误差应控制在+-5mil以内还有飞线未连接时钟要包地处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

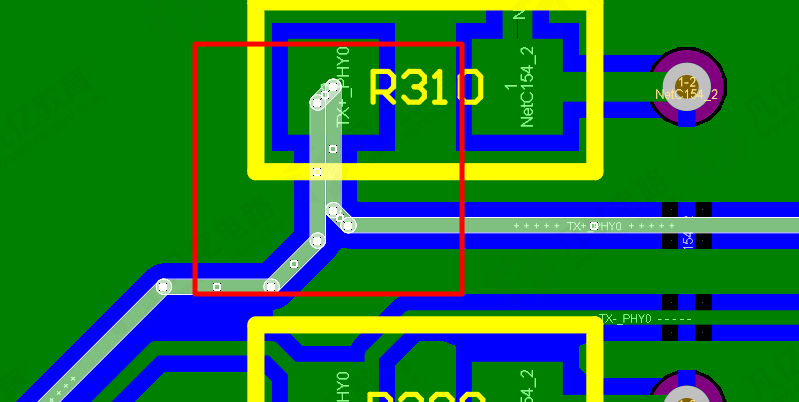

差分连接焊盘走线不要重叠、锐角,两边保持一致变压器除差分走线以外其他所有走线加粗到20mil以上差分走线尽量耦合差分走线出焊盘尽快耦合保持长度一致时钟信号包地打孔处理rx、tx分别建立等长组控制100mil误差分别等长走线应连接到焊盘中心,

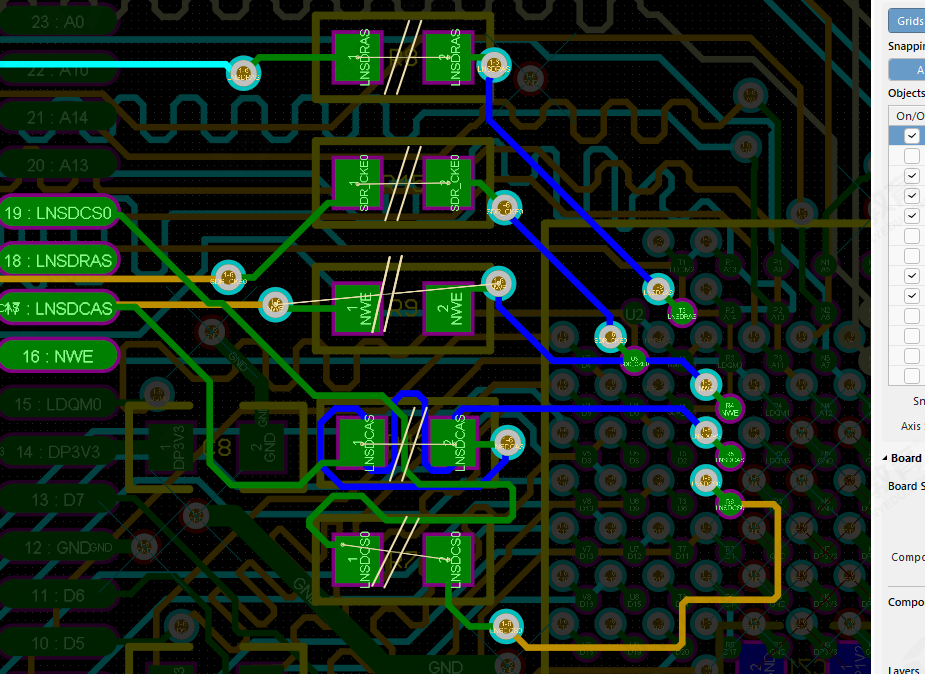

时钟线要包地处理变压器的线除了差分外其他的都要大于20mil这里的差分可以优化一下,线要连到焊盘中心晶振下面不要走线 这里除了跨接器件所在的地方其他的都要保持2mm的间距以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

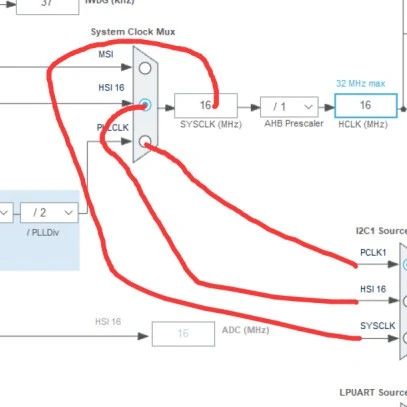

1,低速时钟LSE是外部晶振作时钟源,主要提供给实时时钟模块,所以一般采用32.768KHz。LSI是由内部RC振荡器产生,也主要提供给实时时钟模块,频率大约为40KHz。(LSE和LSI)只是提供给芯片中的RTC(实时时钟)及IWDG(独立看门狗)使用。 2,中速时钟MSI RC

变压器除差分以外所有走线加粗到20mil多处走线锐角,尽量避免走线、铺铜锐角多处尖岬铜皮、孤岛铜皮,器件中间多余尖细铜皮挖空处理时钟信号包地打孔处理差分对内控制5mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处drc7.时钟信号包地,尽量

多处存在开路报错焊盘应从短边出线,避免从长边和四角出线ddr和芯片放置太近,导致没有足够空间绕线,绕线很乱走线不能从同层器件中间穿过时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

随着科技的快速发展,高速信号逐渐替代低速信号,成为许多电子系统的最佳选择,然而高速信号最大的缺点在于其稳定性和可靠性不如低速信号,这就需要靠走线系统来弥补。那么如何走线,保证高速信号的质量?1、屏蔽规则在高速PCB设计中,时钟等关键高速信号

扫码关注

扫码关注