- 全部

- 默认排序

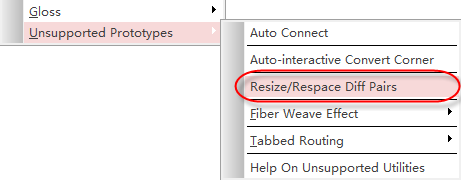

答:我们在PCB设计完成之后,PCB中的差分信号线宽线距已经决定好了,有时候会因为一些阻抗的变化或者叠层的变化,是差分信号的线宽线距会发生变化,我们需要对差分的线宽线距进行修改,手动去修改会比较麻烦,这里讲解一下,如何对差分信号的线宽线距进行自动调整,具体操作如下所示:

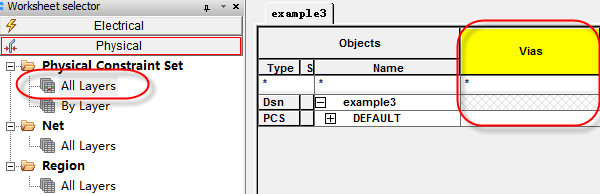

答:在进行PCB设计时,都必须使用到过孔,对走线进行换层处理。在走线进行打过孔之前,必须先要添加过孔,这样在PCB布线时才可以使用过孔,具体操作的步骤如下所示;

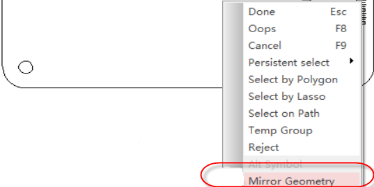

答:一般结构工程师在绘制结构图纸的时候,都会有顶视图与底视图之分,我们导入到PCB之后,是需要将底视图左右镜像处理的,因为PCB里面的背面是从正面透视看过去的,所以将底视图镜像之后,就是是跟PCB界面是一致的,对底层的DXF文件镜像处理的操作步骤,具体如下所示:

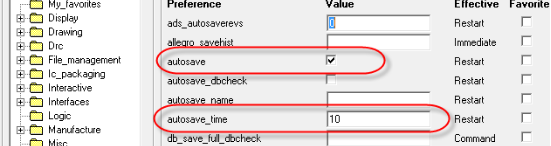

答:在进行PCB设计的的时候,为了防止突发状况的发生,一般都会进行随时保存,做久了以后还是会忘记去保存,所以Allegro软件提供了自动保存的功能,这里我们讲解一下如何进行自动保存,以及自动保存的时间如何设置,,具体操作如下:

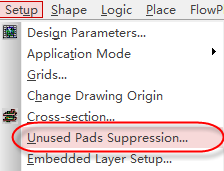

答:做无盘设计的目的,是因为通孔的焊盘在内电层,是具有寄生电容的效应的,容易造成阻抗的不连续,导致信号出现发射,从而影响信号的完整性,所以在处理高速信号时候,在PCB设计端就将走线连接层的焊盘去掉,最大程度的保持地过孔与通孔连接处的走线阻抗一致,具体操作的步骤如下所示:

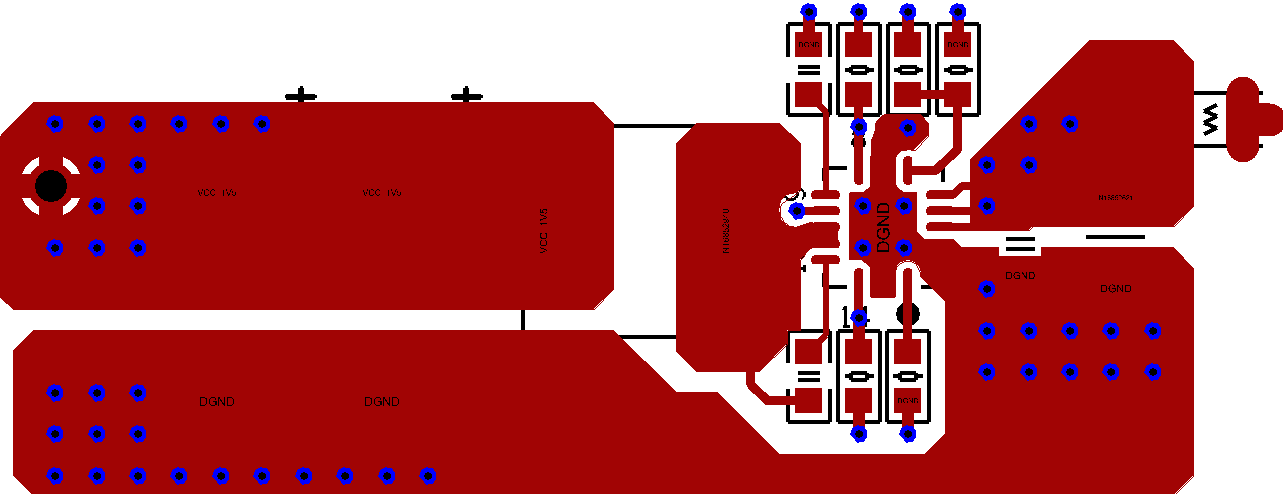

答:在Allegro软件中,所铺的铜皮全部都是动态铜皮,在进行Etch显示的时候,包括走线、铜皮都会显示,在前面的问答中我们讲解了如何将铜皮全隐藏不显示,但是,这样不方便走线设计,走线时不清楚哪一块有铜皮,这里我们讲解一下,如何设置铜皮不显示,但是在PCB中还是显示铜皮的边框,具体操作如下所示:

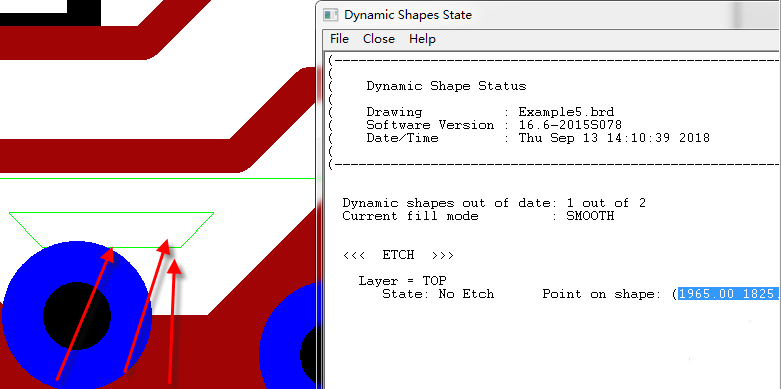

答:我们在设计完成之后,需要对所有的铜皮进行smooth处理,在进行smooth处理的时候,有时因为铺铜的错误操作,出现有一块或者几块铜皮不能更新,出现Out of data shape的问题,如图6-188所示,

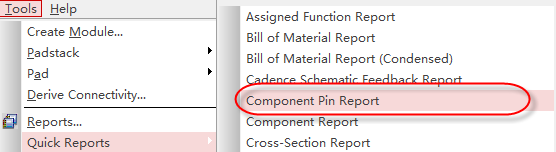

答:我们输出贴片坐标文件,执行File-Export,选择Placement,输出的坐标文件,输出的文件是文本文件,为了贴片更方便一些,我们这里讲解下如何从Allegro软件中导出Excel格式的贴片坐标文件,操作如下:

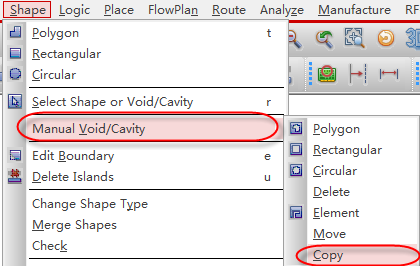

答:我们这里所说的铜皮避让区域,一般指的是手动去对铜皮进行修整过的地方。在处理相同模块的时候,这个手动进行调整过的地方是可以进行复制的,这里讲解一下,如何对修整好的铜皮避让区域进行复制以及其它操作,具体如下:

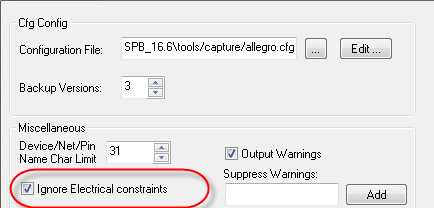

答:我们在进行PCB设计的时候,都是在PCB布局完成之后,在PCB中进行规则设置,但是很多原理图工程师喜欢在原理图中设置规则,这样导入网表之后,PCB加入的规则就会被冲掉,我们这里讲解一下,如何不将原理图的中所添加的规则导入到PCB中,具体操作的步骤如下所示:

扫码关注

扫码关注