- 全部

- 默认排序

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在verilogHDL描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

怎么学单片机?也常看到有人说学了好几个月可就是没有什么进展。当然,受限于每个人受到的教育水平不同和个人理解能力的差异,学习起来会有快慢之分,但我感觉最重的就是学习方法。一个好的学习方法,能让你事半功倍,这里说说我学习单片机的方法。 1、万事开头难、要勇敢迈出第一步。

一般我们会在Allegro软件中指定这几个与封装库有关的路径。第一步,点击Allegro软件的Setup命令的最后一项User Preferences...,如图4-25所示; 图4-25 用户参数设置示意图第二步,在弹出的对话框中,选择Library中的devpath、padpath、psmpath三项设置路径,如图4-26所示; 图4-26 封装库路径指定示意图Ø Devpath:第三方网表(Other方式导出的网表)导入PC

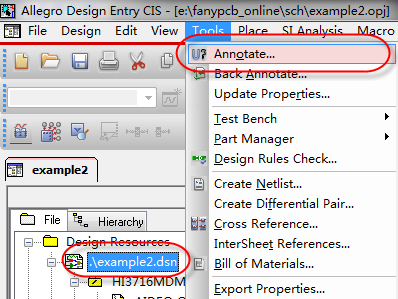

第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑; 图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有

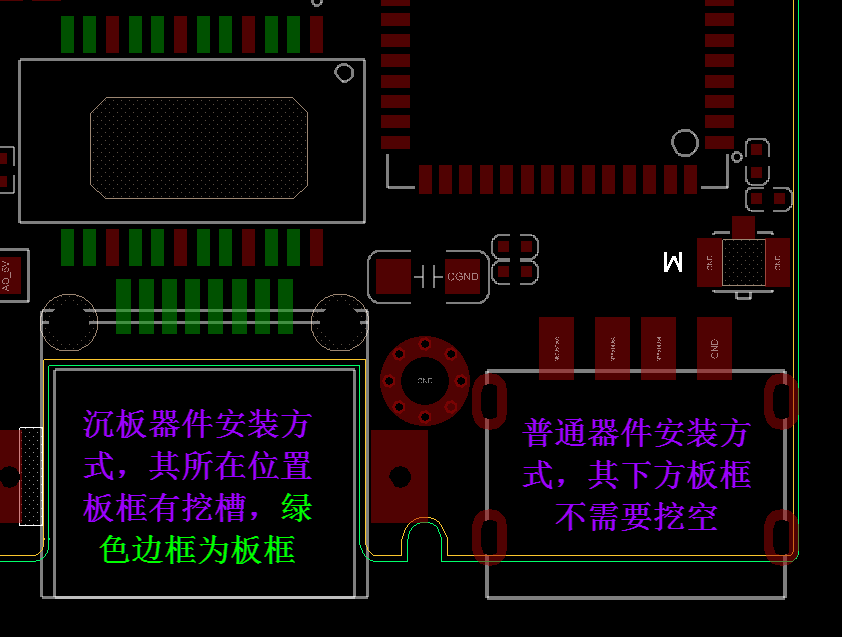

沉板器件即器件的管脚不是在其底部位置,是在它本体的中间位置,不像常规的器件一样,直接可以安装到PCB板子上,而是需要在PCB板子上进行挖槽处理,将其凸起的部分透过PCB板,让其管脚可以正常地贴装到PCB板子上,如图4-77所示: 图4-77 沉板器件处理示意图需要沉板处理的器件封装一般可按以下方法进行:Ø 开孔尺寸:器件四周开孔尺寸应保证比器件最大尺寸单边大0.2mm(8mil);保证能正常放进去。Ø 开孔尺寸标注:开孔标注通常标注在Board_Geom

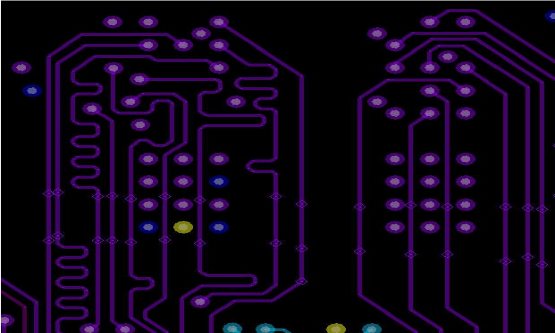

对一些做好的模块进行创建Groups组的操作,方便我们进行模块复用、布局操作。我们创建了Groups组之后呢,这个属性会一直存在,我们是否可以将这个属性给去除掉,方便后期的布线操作与规划。因为添加了这个Groups组的属性以后,从这个模块走出的线会出现下面的小方块的现象,如图6-22所示,虽然不影响整体的性能,但是影响美观,所以呢,这里我们会讲解一下如何将已经创建好的Groups组进行打散的操作,具体操作如下: 图6-22 走线小方块示意图第一步,需要将Allegro软件的

扫码关注

扫码关注