- 全部

- 默认排序

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

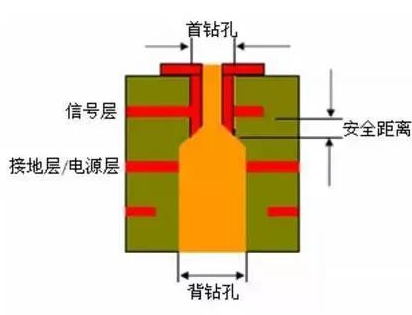

答:背钻其实就是控深钻比较特殊的一种,在多层板的制作中,例如12层板的制作,我们需要将第1层连到第9层,通常我们钻出通孔(一次钻),然后陈铜。这样第1层直接连到第12层,实际我们只需要第1层连到第9层,第10到第12层由于没有线路相连,像一个柱子。这个柱子影响信号的通路,在通讯信号会引起信号完整性问题。所以将这个多余的柱子(业内叫STUB)从反面钻掉(二次钻)。所以叫背钻,但是一般也不会钻那么干净,因为后续工序会电解掉一点铜,且钻尖本身也是尖的。所以PCB厂家会留下一小点,这个留下的STUB的长

答:屏蔽罩,就是用来屏蔽电子信号的工具。由支腿及罩体组成,支腿与罩体为活动连接;罩体呈球冠状。主要应用于手机,GPS等领域,是防止电磁干扰(EMI)、对PCB板上的元件及LCM起屏蔽作用。屏蔽罩的材料一般采用0.2mm厚的不锈钢和洋白铜为材料,其中洋白铜是一种容易上锡的金属屏蔽材料。屏蔽罩的作用主要有以下几点:用屏蔽体将元部件,电路,组合件,电缆或整个系统的干扰源包围起来,防止干扰电磁场向外扩散;用屏蔽体将接收电路,设备或系统包围起来,防止它们受到外界电磁场的影响;屏蔽静电、防止电磁干扰、对电子

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

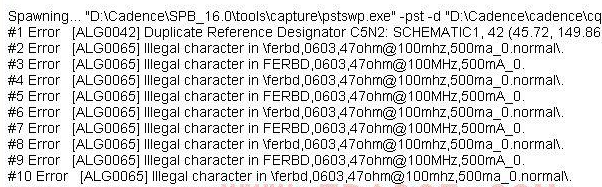

答:orcad当前设计中,所用到库在原理图页面下方的Design Cathe里,在绘制原理图时,可能很多部分是从别的原理图拷贝而来,所以Design Cathe中就会存在一些非法字符,从而影响网表的输出,我们就需要将Design Cathe中的非法字符消除,消除的步骤如下:第一步,点击菜单File→New Library,新建一个库在当前设计的路径下,注意保存的时候不要在路径上出现非法字符,如含有括号、百分号等;第二步,在Design Cathe中找到库路径中含有非法字符的那个库文件,选中库文件

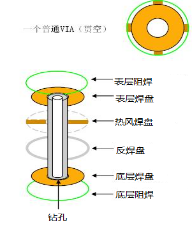

答:一般Allegro软件焊盘由Regular Pad、Thermal Relief、Anti Pad、Soldermask、Pastemask这几项组成,具体的焊盘含义如下,整个焊盘的剖面如图4-21所示:Ø Regular Pad:规则焊盘,在正片中看到的焊盘,也是基本的焊盘;Ø Thermal Relief:热风盘,也叫花焊盘,在负片中有效,设计用于在负片中焊盘与敷铜的接连方式,防止焊接时散热太快,影响工艺;Ø Anti Pad:隔离焊盘,用来控制负片工艺中内

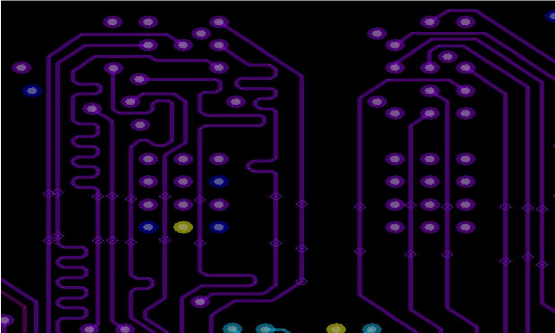

答:在前面的几个问答当中,我们都有提到,对一些做好的模块进行创建Groups组的操作,方便我们进行模块复用、布局操作。我们创建了Groups组之后呢,这个属性会一直存在,我们是否可以将这个属性给去除掉,方便后期的布线操作与规划。因为添加了这个Groups组的属性以后,从这个模块走出的线会出现下面的小方块的现象,如图6-22所示,虽然不影响整体的性能,但是影响美观,所以呢,这里我们会讲解一下如何将已经创建好的Groups组进行打散的操作,具体操作如下:

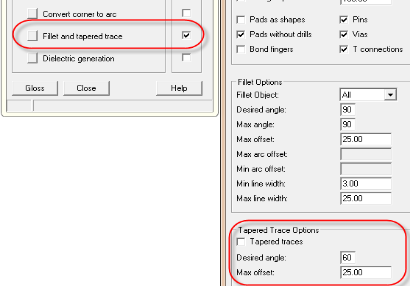

答:所谓渐变线,是添加在走线线宽突变的地放,来降低线宽变化引起的阻抗突带来的信号反射的影响,其功能与泪滴是差不多的,具体操作如下:第一步,需要设置好参数,点击执行菜单命令Route-Gloss,在下拉菜单中选择Parameters,进行参数设置,如图6-157所示;

答:我们在PCB设计过程中,一把布线的顺序是先走信号线,然后进行电源的处理、电源的分割,然而电源的飞线是非常多的,非常影响信号线的布线,所以刚开始会将电源的飞线进行隐藏,具体操作的步骤如下所示:

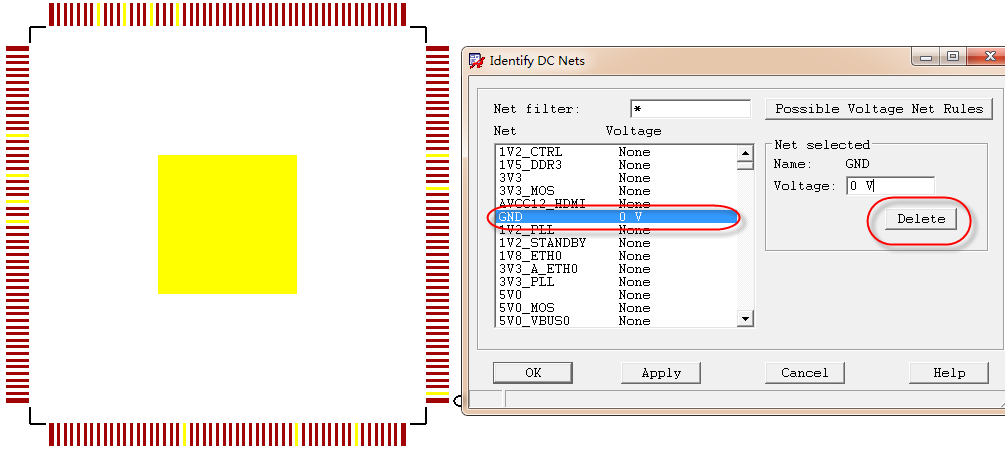

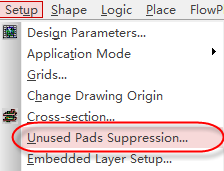

答:做无盘设计的目的,是因为通孔的焊盘在内电层,是具有寄生电容的效应的,容易造成阻抗的不连续,导致信号出现发射,从而影响信号的完整性,所以在处理高速信号时候,在PCB设计端就将走线连接层的焊盘去掉,最大程度的保持地过孔与通孔连接处的走线阻抗一致,具体操作的步骤如下所示:

扫码关注

扫码关注