- 全部

- 默认排序

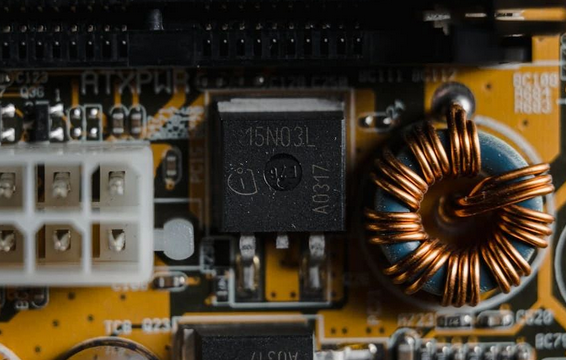

在通信系统中,相比单端电路,许多工程师会更加乐意差分电路,因为差分电路有更高的线性度、抗共模干扰信号性能等,当然差分电路并非没有缺点,所以可以通过改善差分滤波器来降低其缺点影响。1、成对差分走线的长度须相同2、差分对内的走线布线须彼此靠近3

在电路设计中,电磁兼容性(EMC)是确保设备稳定运行、减少电磁干扰的关键。其中,信号线的处理对于提升EMC性能至关重要。下面将谈谈信号线该如何设置。1、拉大距离确保信号线周围无其他辐射能量源,特别是附近的布线及印刷板布局。如发现干扰,拉大信

1. 问题描述某款产品辐射发射超标,据测试人员反应,前期刚刚转产的同系列产品测试情况良好,该产品与前期转产的产品硬件基本一致,只是在功能配置上略微精简,少一些功能,主板是同一款印制电路板。2. 分析过程 图一:整改前辐射发射测试图为了发现问题,初步进行了如下实验1)、判断是否与信

如果成为了电子工程师,总会少不了高频PCB设计,既要确保信号的完整性,也要减少干扰,提高系统的可靠性,很难实现。要想高频PCB设计好,布线是必不可少的,下面谈谈有哪些布线技巧是值得学!1、多层板布线设计使用至少四层板,包括顶层、底层、电源层

在PCB设计中,布局布线和电路性能息息相关,不正确的走线设计,尤其是信号线长度与信号频率之间不匹配,容易引发谐振干扰,进而影响电路的稳定性和可靠性,那么这是为什么?1、布线长度与信号波长的关系当信号线的长度恰好为信号波长的1/4或其整数倍时

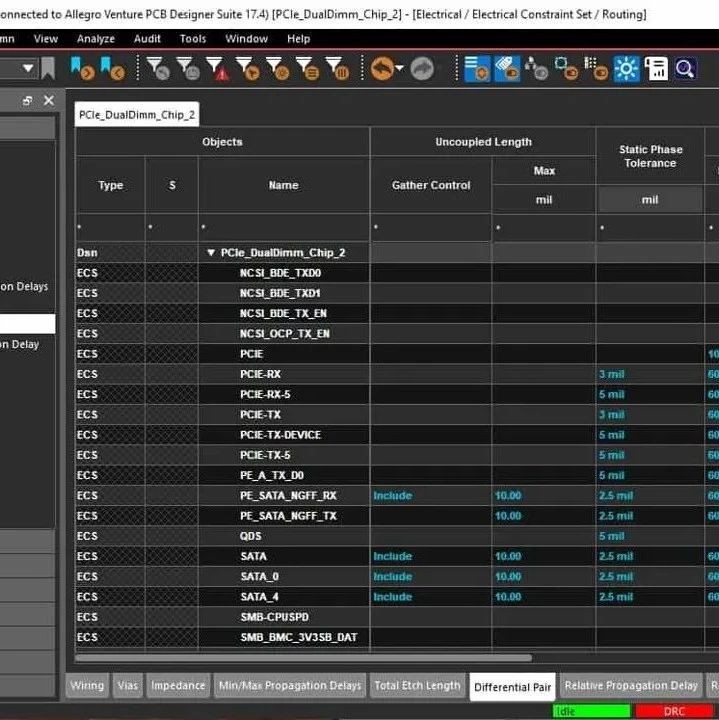

本文要点PCB 差分对的基础知识。差分对布线指南,实现更好的布线设计。高效利用 PCB 设计工具。“众人拾柴火焰高” ——资源整合通常会带来更好的结果。毕竟 “三个臭皮匠,顶个诸葛亮”,在电子领域也是如此:较之单一的走线,差分对布线更受青睐。不过,差分对布线可能没那么容易,因为它们必须遵循特定的规则

本文要点电子产品中有许多噪声源,可能出现在系统内部和外部。噪声耦合抑制技术在电路设计层面和物理布线中实施,以抑制特定的噪声源。可以通过布线前和布线后仿真来评估噪声耦合抑制技术的有效性。任何在示波器上仔细观察过低电平信号读数的人都会熟悉电子电路中可能出现的噪声。出现的各种固有的噪声源在低信号电平下十分

在高速PCB(印制电路板)布局布线中,网格系统不仅是设计的基础框架,更是确保信号完整性、优化布线效率及减少资源消耗的关键因素。不过有很多人不太清楚网格系统的作用,下面将说说。1、确定布线通道网格系统为设计者提供了明确的布线通道,避免布线时随

在单板设计中,需要密切关注接地部分,其中接口器件的接地是至关重要的,它直接影响到系统的稳定性和电磁兼容性,不当的接地设计可能导致信号质量下降,出现误码、丢包等,还可能成为电磁干扰源,向外辐射噪声。1、分割接口地单独划分出一块区域作为接口地,

虽然工程师很少撞见关于大电流的电路设计,但如果碰见了,其走线是需要耗费许多心血,若是走线处理不当,很容易导致发热、电阻增大甚至线路烧毁等,需要采取具体措施解决!1、设置焊盘属性走线将需要处理的大电流走线设置为焊盘属性,确保线路板制造时该走线

扫码关注

扫码关注