- 全部

- 默认排序

答:一般处理模拟地、数字地的方法有以下几种:直接分开,在原理图中将数字区域的地连接为DGND,模拟区域的地连接为AGND,然后PCB中的地平面分割为数字地与模拟地,并吧间距拉大;数字地与模拟地之间用磁珠连接;数字地与模拟地之间用电容连接,运用电容隔直通交的原理;数字地与模拟地之间用电感连接,感值从uH到几十uH不等;数字地与模拟地之间用零欧姆电阻连接。总结来说,电容隔直通交,造成浮地。电容不通直流,会导致压差和静电积累,摸机壳会麻手。如果把电容和磁珠并联,就是画蛇添足,因为磁珠通直,电容将失效。

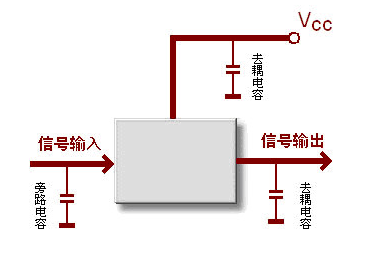

答:可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。 去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电

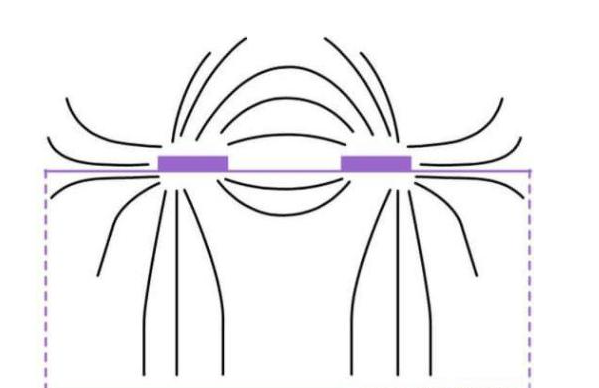

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

答:零欧姆电阻又称为跨接电阻器,是一种特殊用途的电阻,0欧姆电阻的并非真正的阻值为零,欧姆电阻实际是电阻值很小的电阻。正因为有阻值,也就和常规贴片电阻一样有误差精度这个指标。电路板设计中两点不能用印刷电路连接,常在正面用跨线连接,这在普通板中经常看到,为了让自动贴片机和自动插件机正常工作,用零电阻代替跨线。零欧姆电阻的作用有如下几种:Ø 在电路中没有任何功能,只是在PCB上为了调试方便或兼容设计等原因;Ø 可作跳线使用,避免用跳针造成的高频干扰(成为天线);Ø 在匹

答:常规的基板板材的性能参数有如下几种:Tg,玻璃化转变温度,当温度升高到某一区域时,基板将由“玻璃态”转变成为“橡胶态”,此时的温度我们就称之为玻璃化转变温度;Td,分解温度,表示印制板基材的热分解温度,是指基材的树脂受热失重5%时的温度,作为印制板的基材受热引起分层和性能下降的标志;CTE,热膨胀系数,物体由于温度改变而有胀缩现象。其变化能力以等压(p一定)下,单位温度变化所导致的长度量值的变化,即热膨胀系数表示;CTI,相对漏电起痕指数,基材在表面经受住50滴电解液,一般是0.1%氯化铵水

答:上拉、下拉电阻的作用有如下几种:提高电压准位:当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的搞电平值;加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻;N/A pin防静电、防干扰:在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗, 提供泄荷通路。同时管脚悬空就比较容易接受外界的电磁干

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

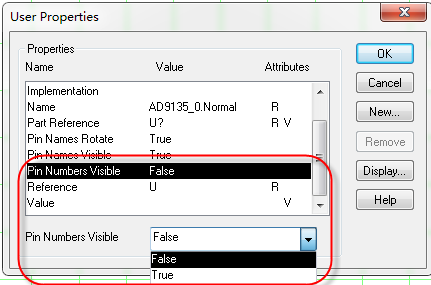

答:在设计的时候,有一些原理图符号不需要将管脚编号显示,比如电阻、电容、二极管等元器件,我们的操作方法如下:第一步,打开所要隐藏管脚编号的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中选中Pin Numbers Visble,修改Value值属性即可;第三步,需要显示管脚编号的,Value值那一栏选择True;隐藏管脚编号的,Value值那一栏选择False,如图2-48所示: 图2-48 隐藏与显示管脚编号示意图

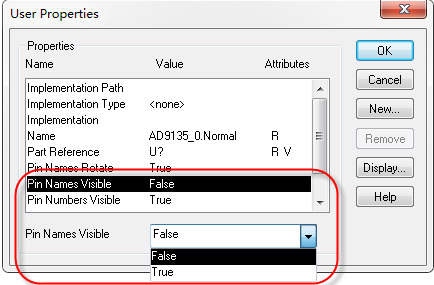

答:在设计原理图库的时候,除了IC类器件需要显示网络的名称以外呢,一般其它的原理图库是不需要显示网络名称的,主要是显示器件内部的连接关系,所以我们需要隐藏掉原理图库中的网络名称,操作步骤如下:第一步,打开所要隐藏网络名称的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中选中Pin Names Visble,修改Value值属性即可;第三步,需要显示网络名称的,Value值那一栏选择True;隐藏网络名称的,Value值那一栏选择False,如图2-

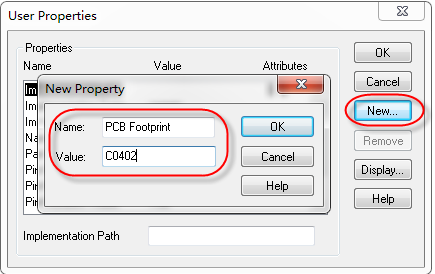

答:这里我们分为两种情况进行分析,一种是在绘制原理图库的时候,怎么显示与隐藏元器件封装名称;另外一种是在绘制原理图的时候,怎么显示与隐藏元器件封装名称。① 绘制原理图库时隐藏PCB封装的操作步骤如下;第一步,打开所要隐藏PCB封装名的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中点击右侧New…,新建属性,Name填写PCB Footprint,Value值填写相对应的封装名,如图2-50所示;第三步,选中新加的PCB Footprin

扫码关注

扫码关注