- 全部

- 默认排序

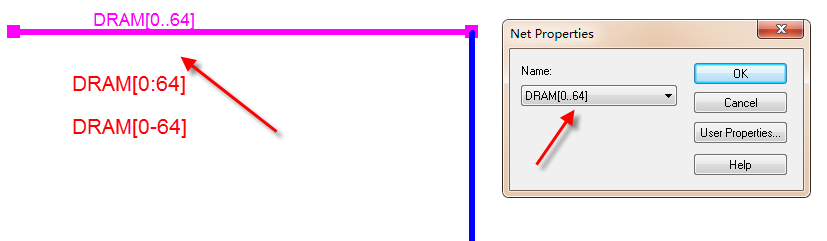

答:在前面的问答中,我们已经创建好总线了,创建好总线以后,我们需要在总线上放置好总线的名称,也就是网络标号,按照网络一一对应,总线的命名方式分为三种,如下列:Busname[0..64],其中Busname是总线名称,0到64是总线中包含的分支数目;Busname[0 :64],其中Busname是总线名称,0到64是总线中包含的分支数目;Busname[0-64],其中Busname是总线名称,0到64是总线中包含的分支数目。我们在命名总线的时候,放置的是网络标号net Alias,点击菜单P

答:在orcad中使用Bus总线的时候,有以下几个注意事项,如下列:总线不是强制使用的,不使用总线也是可以的,使用总线构架是使得原理图更加清晰,分析原理图更加透彻;总线与信号分支之间的连线只能通过网络标号net Alias来进行电气连接,否则是连接不上的;如果不使用总线入口Bus Entry来进行连接,直接将信号分支连接到总线上,在连接也会显示连接点,但是这样信号与总线是没有真正连接上的,一定要通过Bus Entry的方式来连接总线与信号分支;总线的命名方式一定要按照前面的问答中所要求的那样,三

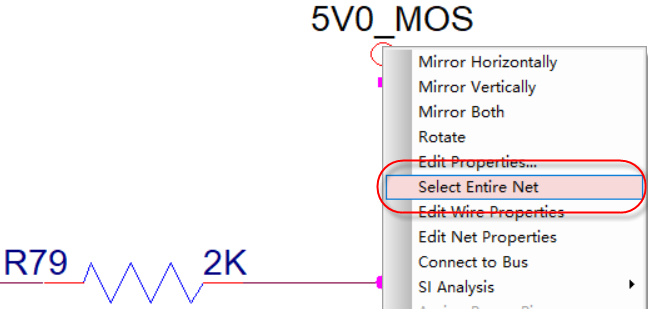

答:第一步,打开任意一页原理图,单击左键选中一个网络,然后单击鼠标右键,选择Select Entire net,进行网络点亮,如图3-40所示: 图3-40 网络高亮设置示意图第二步,选择Select Entire net以后,回到原理图的界面,可以看到所有的这个网络的连线都显示高亮的颜色,如图3-41所示; 图3-41 网络高亮显示示意图第三步,为了方便查看,高亮的颜色即选中的颜色是可以更改的,执行Options→Preferences…菜单,选择Colors即可进行更改,

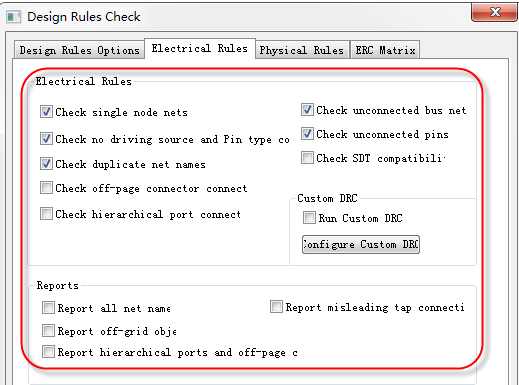

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

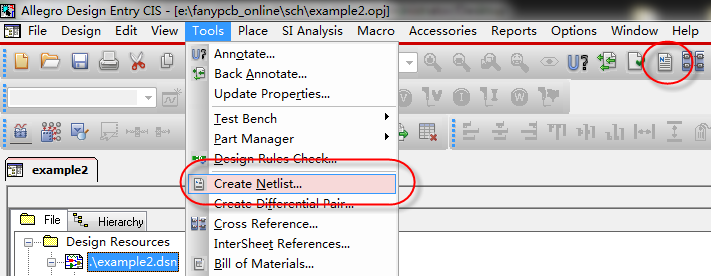

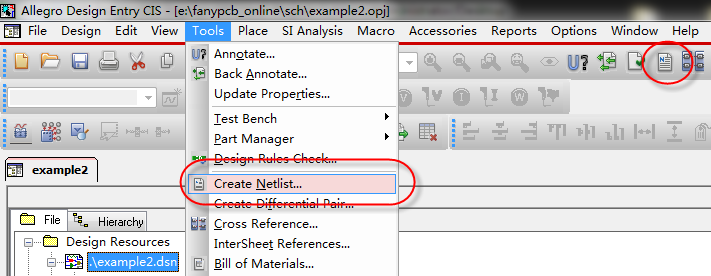

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

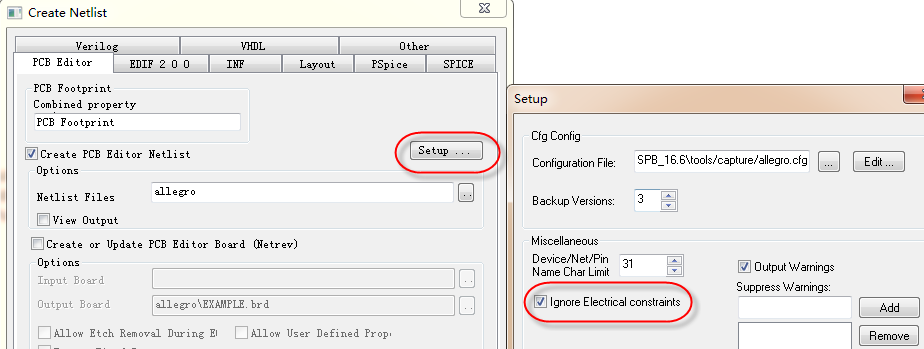

答:我们在进行PCB设计的时候呢,尽量不要把原理图的规则导入到PCB中,我们需要在输出网表的时候进行设置,具体的操作步骤如下所示:第一步,选中原理图的根目录文件即DSN文件,进行网表的输出,执行菜单Tools-Create netlist,创建网表;第二步,在弹出的输出PCB网络表的对话框中,其它地方都是不用勾选的,在右侧有一个Setup选项,是输出网络的参数设置按钮,我们需要在这里进行不输出原理图规则的设置;第三步,点击输出网表的Setup选项,进行参数的设置,如图3-211所示,在左侧箭头所

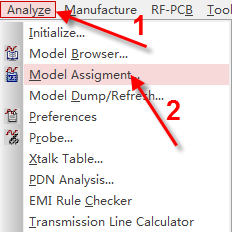

答:所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:

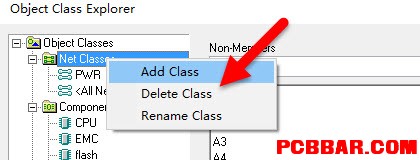

答:我们在Allegro中进行设计的时候,总会遇到这样的问题,创建类的时候,可供选择的选项太多,这里我们对这些不同的类做一个说明:

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注