- 全部

- 默认排序

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:在设计原理图时,工程师们都喜欢在原理图中加上自己的独有标志或者是公司的logo,来表示这份原理图是该工程师绘制的或者是该公司的产品,这里我们就教一下大家,如何将公司的logo加入的原理图的Title Block中,具体的操作如下:第一步,Title block是一个全局的变量,存在于每一页的原理图中,我们需要在库里面的Title block加入图片,然后更新到原理图中;第二步,在当前设计的库Design Cathe路径下找到Title block的库,复制到本地的库路径下,才可以对其进行更改

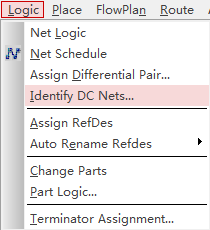

答:打开Allegro软件,点开logic菜单栏,如图5-27所示,这是铜箔操作菜单栏下一些命令行。下面我们对logic菜单栏下面的一些常用命令进行简单的介绍,具体知道是如何进行操作的,具体如下:

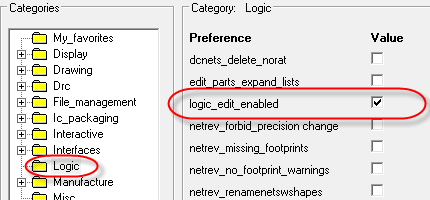

答:在第375问中我们讲解了如何手动去添加元器件,这样直接添加的元器件本身是没有网络的,这一问呢,我们讲述一下如何手动的在PCB中去修改网络与添加网络,具体操作的步骤如下所示:首先,要勾选允许元器件编辑与网络的选项,才可以进行进行编辑,进入用户参数设置,选择logic,将logic edit enabled选项勾选上,如图6-135所示;

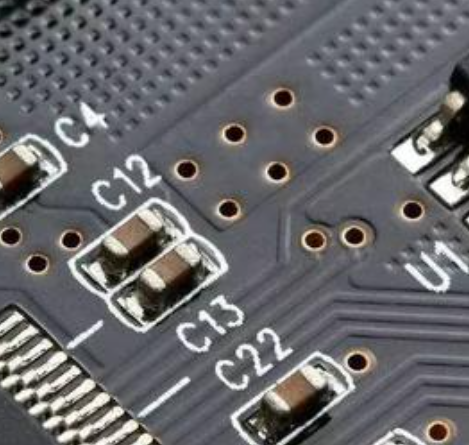

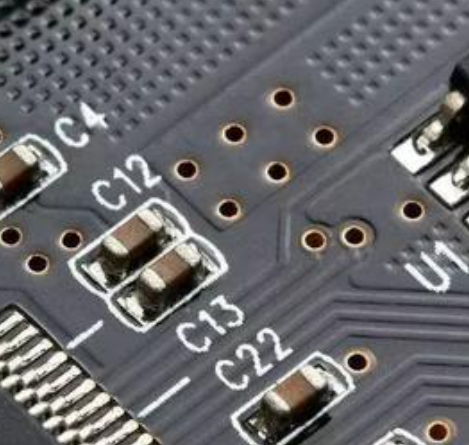

答:SMT是Surface Mount Technology的缩写,是表面组装技术,是目前电子组装行业里最流行的的一种技术和工艺,是一种无需在印制板上钻插装孔,直接将表面组装元器件贴、焊到印制电路板表面规定位置上的电路装联技术。

答:SMD是Surface Mounted Devices的缩写,是意表面贴装器件,它是SMT(Surface Mount Technology)元器件中的一种。

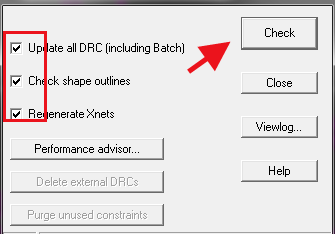

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种:当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单栏命令“To

PLC与单片机的本质区别

PLC控制系统,Programmable logic Controller,可编程逻辑控制器,专为工业生产设计的一种数字运算操作的电子装置,它采用一类可编程的存储器,用于其内部存储程序,执行逻辑运算,顺序控制,定时,计数与算术操作等面向用户

1 FPGA学习重点1. 看代码,建模型只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的

MentorPADS作为PCB设计软件之一,也是工程师们常用的EDA软件之一,所以小白初入PCB设计行业,了解PADS软件的使用方法是很有必要的,今天将分享PADS软件的快捷键大全。PADS是一款制作PCB板的软件,其中包括PADS log

扫码关注

扫码关注