- 全部

- 默认排序

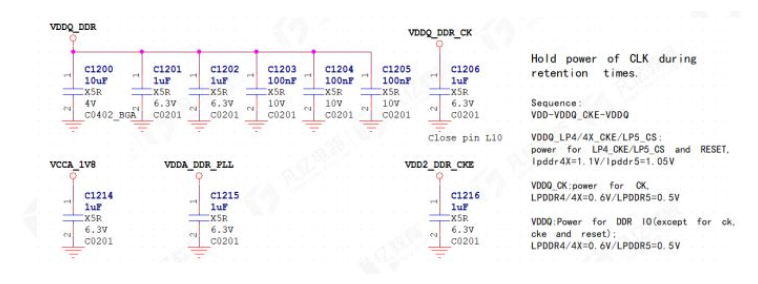

ddr电路简介RK3588 ddr 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPddr4/LPddr4X/

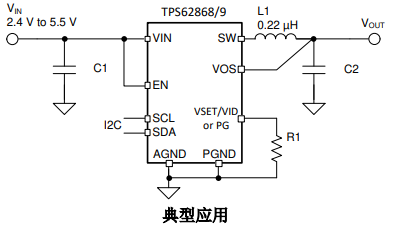

一、典型应用• 为 FPGA、CPU、ASIC 或视频芯片组提供内核电源• IP 网络摄像头• 固态硬盘• 光学模块• LPddr5 VDDQ 轨电源二、规格1、TPS6286900CRQYR 降压 开关稳压器 IC REG BUCK PR

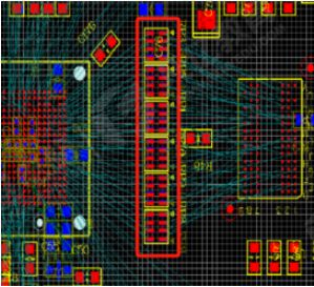

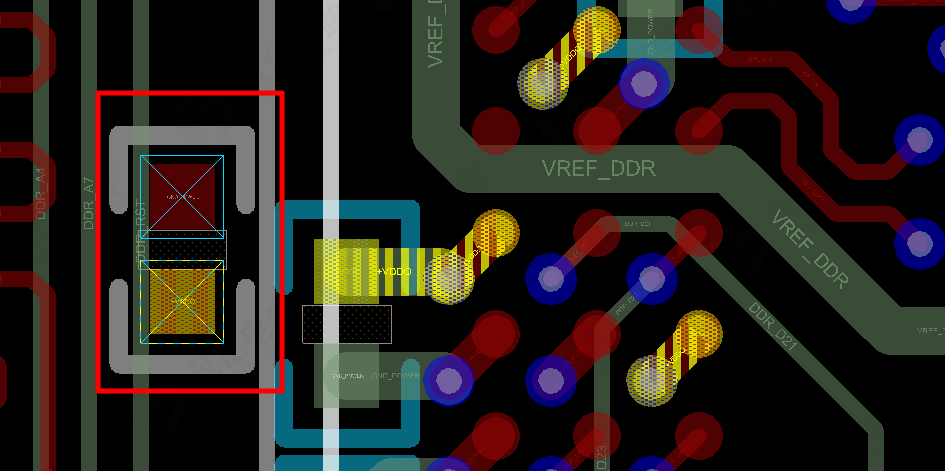

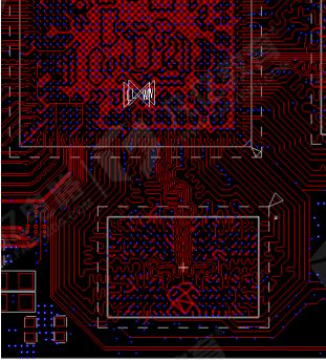

RK3588 VCC_ddr电源PCB设计1、VCC_ddr覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VCC_ddr的电源在外

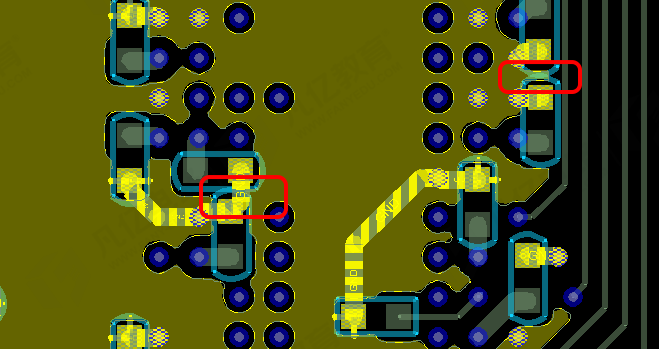

一般我们在进行PCB设计时可能会留意到有些信号会串联一个电阻,那么大家是否有想过所串联的电阻是有什么作用呢?大家可以看一下下面图示的案例,信号是从CPU处出来再接到ddr颗粒的,每一个ddr数据线都有串联一个电阻,其实这个串联电阻的作用是进

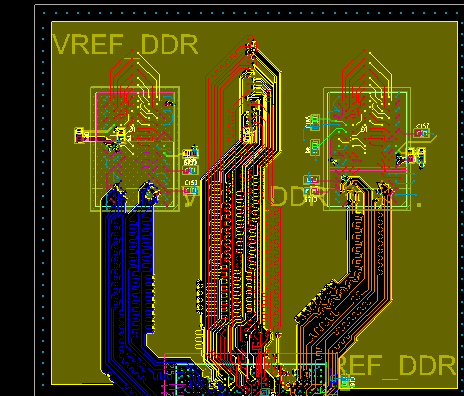

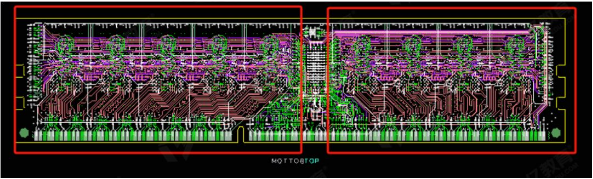

这个vref是参考电压,写入或读取数据时需要用vref来确定是高电平还是低电平,不要大面积铺铜。四块的也是一样ddr到芯片的距离有点远了一般是600-800mil丝印位置可以调一下,调整齐不放焊盘上其他的没什么问题以上评审报告来源于凡亿教育

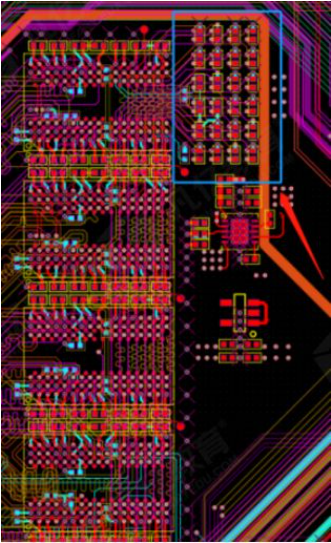

大家如果做过ddr的设计可能会发现在进行多片ddr连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?通常在ddr末端的电阻是为了防止信号反射的,起阻抗匹配的作用,之前我们介绍过另一种防止信号反射的解决措

器件摆放注意不要干涉最多两个电容用一个地过孔过孔不要打到小焊盘数据线等长组以DQS 为基准线,地址线以时钟线为基准线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

ddr采用菊花链拓扑结构时,由于信号传输线较长通常需要在ddr末端加上终端匹配电阻,端接的方式有很多,但是都是为了解决信号的反射问题,通常为了消除信号的反射可以在信号的源端或者终端进行解决,在源端处消除反射是采用电阻串联的方式,在终端处消除

有器件没有布局布线滤波电容放置不均匀,应尽量1-2个焊盘一个电容器件丝印干涉,丝印不要重叠保持一定间距以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

ddr拓扑结构的详细解析

在进行多片ddr设计的时候,通常ddr会存在拓扑结构,下面我们将详细介绍一下各种拓扑结构的区别以以及应用场景。首先我们先介绍一下,当只存在一片ddr的时候通常是采用点对点的连接方式,点对点的布线方式优点是结构简单,阻抗以及时序容易控制,适合

扫码关注

扫码关注