- 全部

- 默认排序

答:在绘制原理图时,需要从库中放置我们的元器件,有时候会发现一个库文件中包含的库太多,一个一个对照,会花费很多的时间,这时候需要我们快速定位到库文件,把器件放置到我们的原理图中。操作的方法如下:第一步,在Libraries列表中选中一个库的列表文件,,单击鼠标左键即可选中该元器件库;第二步,选中库文件以后,上方弹出的Part LiST表中含有所有的库文件,任意用鼠标左键选中一个;第三步,选中以后,按下你想要查询的器件的首字母,这样Part LiST表会自动跳到以该字母开头的库,按上下键就可以快速

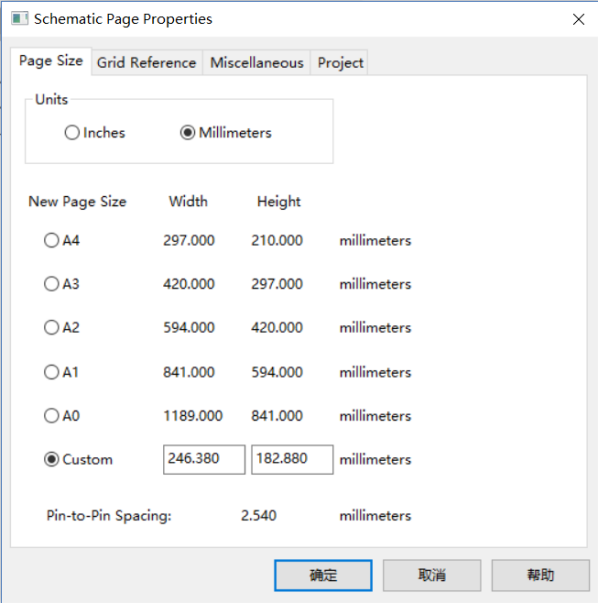

答:1)对原理图单个页面的纸张设计大小的设置方法如下:第一步,在原理图页面上右键,选择菜单Schematic Page Properties,对原理图页面的属性进行设置,如图3-4所示; 图3-4 原理图页面属性设置示意图 图3-5 页面大小属性设置示意图第二步,在弹出的界面中对页面的大小进行设置,Units可以进行单位设置,下面是原理图页面大小设置,在CuSTom中还可以对原理图页面大小进行自定义的设置,如图3-5所示。2)

答:orcad在绘制原理图时,需要从库中把元器件放置到原理图中,放置的方法如下:第一步,执行菜单Place→Part,或者按快捷键P、或者点击右侧菜单栏放置元器件的图标,来调出放置元器件的窗口,如图3-9所示; 图3-9 放置元器件窗口示意图第二步,在放置元器件之前,需要在下面的库路径下指定封装库的路径,如图3-10所示,点击Add Library命令添加库路径; 图3-10 添加库路径示意图第三步,在库路径下选中改元器件库,上面的Part LiST表

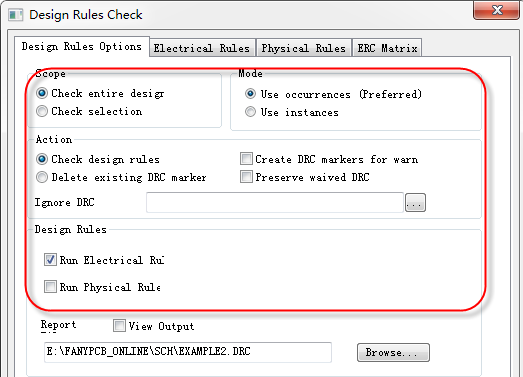

答:orcad进行DRC检测时,如图3-63所示,需要对参数进行设置,每个参数的含义如下所示: 图3-63 DRC参数上设置示意图Check entire design:DRC检查整个原理图;Check Selection:DRC检查选择的部分电路;Use occurrences:选择所有事件进行检查;Use inSTances(preferred):使用当前实体(建议)。所谓实体是指放在绘图页内的元件符号,而事件指的是在绘图页内同一实体出现多次的实体电路。例如,在复杂层次

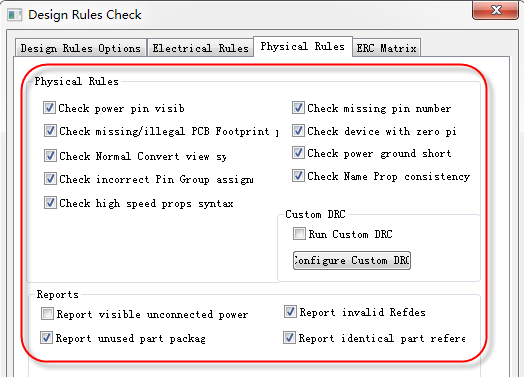

答:orcad进行物理DRC检测时,如图3-65所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-65 物理规则检查参数设置示意图Check power pin visible:检测电源属性的管脚是否显示了管脚名称与编号;Check missing/illegal PCB Footprint:检测封装名称是否填写。是否含有非法字符;Check Normal convert view sySTem:检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同;Ch

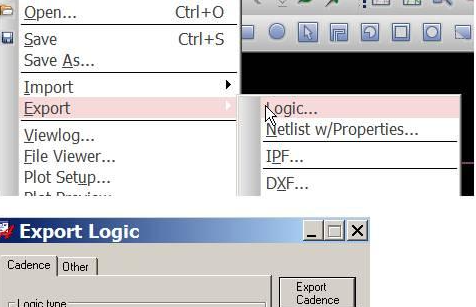

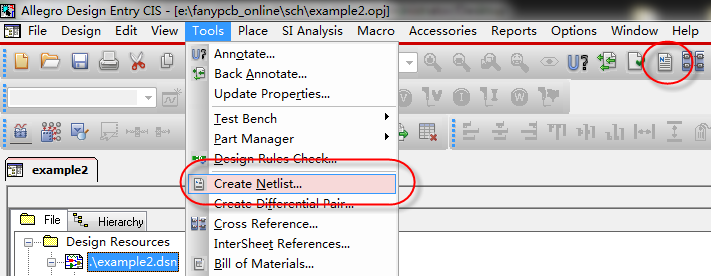

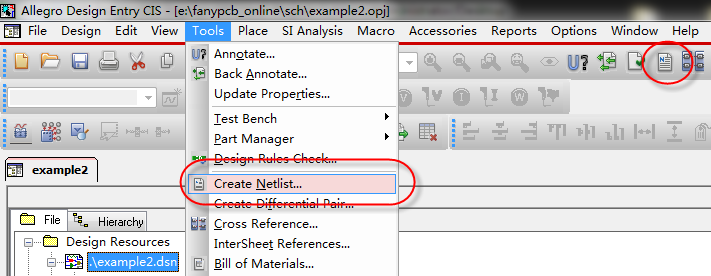

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat NetliST,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat NetliST界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netliST.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat NetliST,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36022): Pin number missing from Pin "1" of Package TEST , P3: SCHEMATIC1, 05.RC5T620-SySTem Power (15.60, 8.00). All pins should be numbered.解决的办法如下所示:第一步,找到管脚缺失的器件P3,然后选中P3这个器件,点击右键,选择Edit Part属性

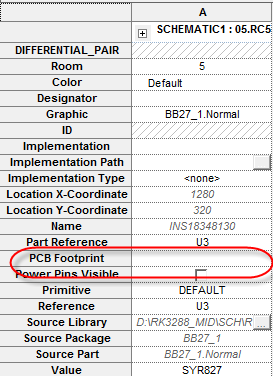

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36002): Property "PCB Footprint" missing from inSTance U3: HI3716MDMO3B_VER_A, ETH PHY_12 (3.95, 1.35).解决的办法如下所示:第一步,错误描述是封装PCB Footprint的缺失,缺失的器件是U3,含义就是U3这个器件在绘制原理图时没有做封装的匹配,这一栏是空的;第二步,在原理图中找到U3这个器件,

扫码关注

扫码关注