- 全部

- 默认排序

ADM2582E/ADM2587E是具备±15 kV ESD保护功能的完全集成式隔离数据收发器,适合用于多点传输线路上的高速通信应用。其内部集成的RS-485驱动器带有一个高电平有效使能电路。

2 GHz带宽!鼎阳科技发布SDS6000 Pro高分辨率高带宽数字示波器新型号-作为国内首款12-bit高分辨率,2GHz高带宽数字示波器,SDS6000 Pro 为高速小信号的测量带来了更多可能性。

2020年1-7月全球动力电池总装机量同比减少16.8%-据外媒报道,近日,韩国新能源市场分析公司SNE Research发布的最新调查结果显示,2020年1-7月全球动力电池总装机量同比减少16.8%,但LG化学、三星SDI、SK创新三大韩企的增长势头依然迅猛。

2020年1-7月全球动力电池总装机量同比减少16.8%-据外媒报道,近日,韩国新能源市场分析公司SNE Research发布的最新调查结果显示,2020年1-7月全球动力电池总装机量同比减少16.8%,但LG化学、三星SDI、SK创新三大韩企的增长势头依然迅猛。

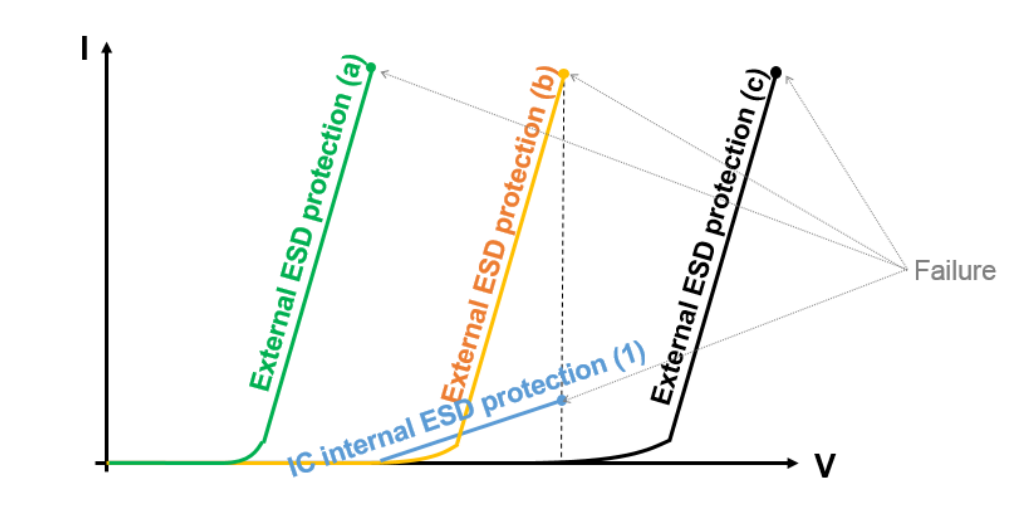

某接地台式产品,对接地端子处进行测试电压为6KV的ESD接触放电测试时,系统出现复位现象。测试中尝试将接地端子与内部数字工作地相连的 Y电容断开,测试结果并未明显改善。

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

扫码关注

扫码关注