- 全部

- 默认排序

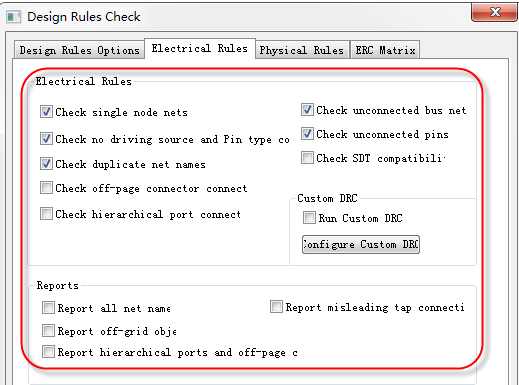

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duPLicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

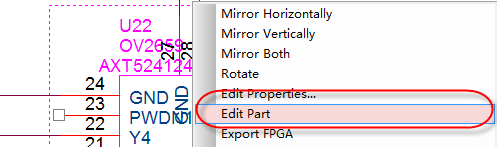

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36041): DuPLicate Pin Name "GND" found on Package LCM0200CE1A0_3 , U22 Pin Number 25: SCHEMATIC1, 23.Camera (129.54, 50.80). PLease renumber one of these.解决的办法如下所示:第一步,找到报错的器件U22,然后选中U22这个器件,点击右键,选择Edi

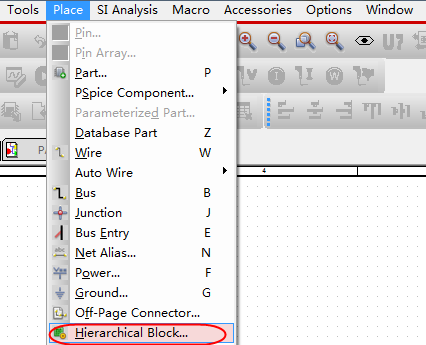

:层次原理图中是有包含的关系,这里我们介绍一下层次原理图自上而下设计思路,按照以下的步骤即可: 第一步,创建分级的模块Hierarchical Block,在原理图设计的页面,执行命令PLace->Hierarchical Block…,如图3-109所示: 图3-109 层次原理图创建分级模块示意图第二步,在弹出的对话框中,输入分级模块的名称,如图3-110所示,选择合适的参数,一般如图3-110所示设置即可,点击OK,则层次式原理图分级模块创建完毕;

答:在层次原理图中,我们之前做好的模块如果是一样的,是可以重复调用的,这样就大大节省了我们设计的时间,特别是有很多重复性的功能模块情况下,下面我们讲解下调用已有模块的方法:第一步,创建分级的模块Hierarchical Block,在原理图设计的页面,执行命令PLace->Hierarchical Block…,如图3-119所示: 图3-119 层次原理图创建分级模块示意图第二步,在弹出的对话框中,输入分级模块的名称,如图3-120所示,选择合适的参数,一般如图3-120

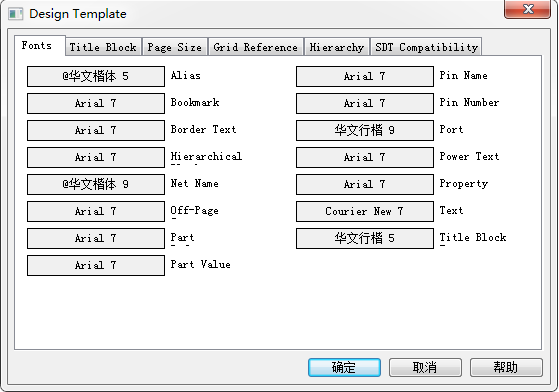

答:我们在运用Orcad进行原理图绘制时候,一般使用的都是默认的字体,用的最多的是就是网络标号的字体、位号的字体、封装属性的字体。当然使用默认字体是没有任何问题的,只是有时候我们将一些属性加以批示与标注,更加醒目这时就需要对其进行更改,一个一个去改费时费力,这里我们讲解下如何批量的去进行更改,具体操作的方法如下:第一步,首先打开原理图,对设计的模板进行更改,这样模板设定好了以后,原理图设计的内容都会根据模板来进行设定,执行菜单命令Options-Design TemPLate,会弹出如图3-13

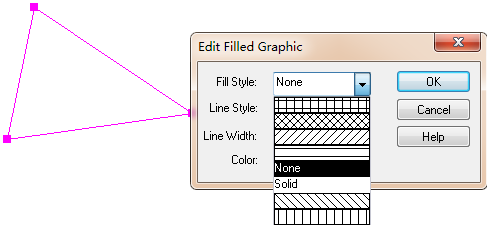

答:我们运用Orcad软件进行标注说明、或者是做原理图库的时候,会使用到实心的可以填充成不同颜色的符号,具体这个是怎么操作实现的呢,我们这里具体的讲解下操作的步骤,不管是绘制原理图的时候,还是绘制原理图封装库,操作的方法都是一致,具体如下:第一步,我们以绘制原理图为例,首先打开一份原理图,执行菜单命令PLace-Polyline,或者是按快捷键Y来放置折线,;第二步,我们在放置折线的时候,这里可以调节这个折线的大小,可以看到我们直接放的折线是按90度去更改的,比较麻烦,这里介绍个小的技巧,按住s

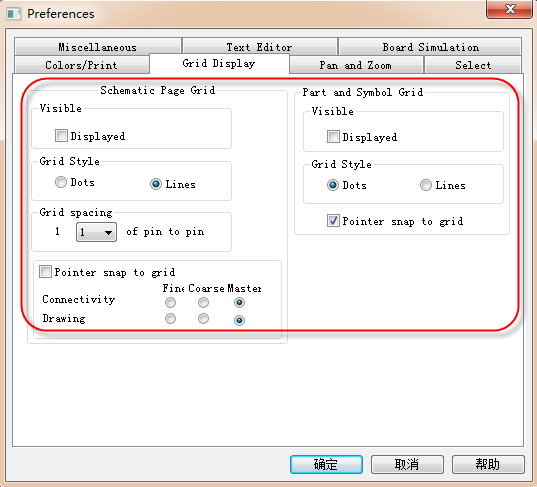

答:我们运用Orcad软件进行原理图的绘制时,也是跟PCB设计的一致的,也是有栅格可以设置,也就是格点的。这样可以快速方便我们进行器件的放置以及原理图中的连线,这里,我们给大家讲解下,这个原理图中栅格的具体的一些设置技巧:第一步,我们需要打开栅格设置的菜单,点击命令栏Options选项,在下拉菜单中选择Preferences,进行参数的设置;第二步,进入Preferences参数设置界面之后呢,需要选择格点显示:“Grid DisPLay”,如图3-222所示,格点显示分为两部分,昨边这部分为“

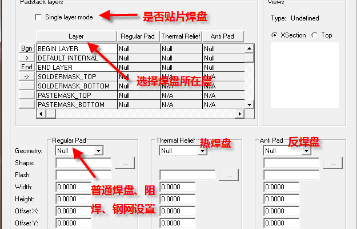

答:Allegro软件中的焊盘制作界面。第一页中,钻孔属性参数的具体含义如下所示,如图4-27所示: 图4-27 焊盘制作钻孔面板参数示意图Ø Units:制作焊盘时使用的单位。Ø Decimal PLaces:设置尺寸时可取的精度到小数点后几位。Ø MultiPLe drill:多孔设置,一般不用。Ø Hole type:钻孔的类型。Ø PLating:钻孔是否为金属化孔。Ø Drill diameter:钻孔的

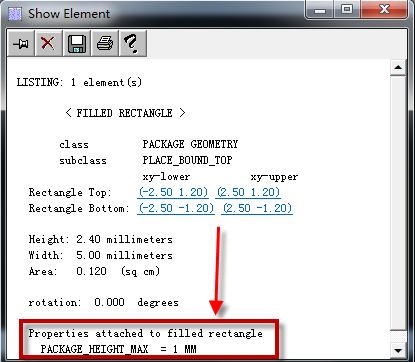

答:在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。第一步,打开一个PCB封装,将Package Geometry-PLace_Bound_top层显示出来,如图4-70所示, 图4-70 显示元器件占地面积示意图第二步,点击Setup-Areas-Package Height选项,如图4-71所示

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-PLace_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, PLace_bound层器件最大外围尺寸(焊盘和丝印中取大值)

扫码关注

扫码关注