- 全部

- 默认排序

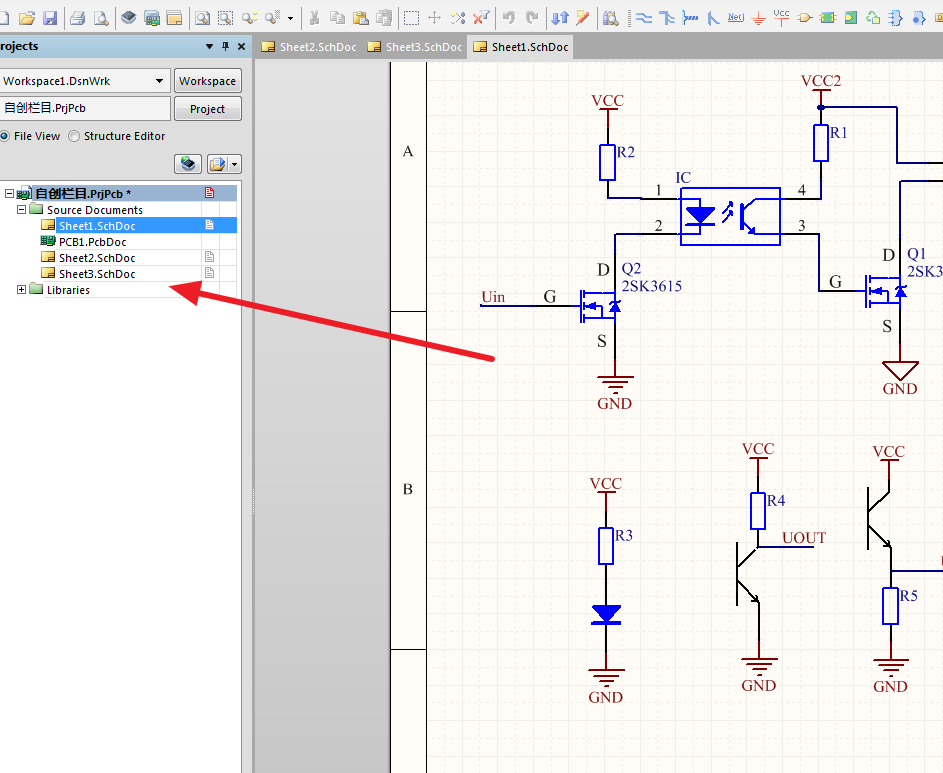

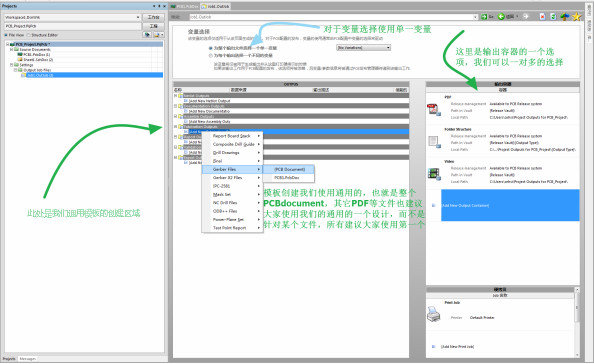

在AD的原理图绘制的时候我们想要只导入部分的原理图或者只导入单独一页的原理图如何进行操作。 这里目前有两种方式,第一种方式是直接放置屏蔽编译框,第二种就是进行网络比对的导入,就是我们使用导入网表比对的方法进行屏蔽部分原理图文件或者某些原理图。

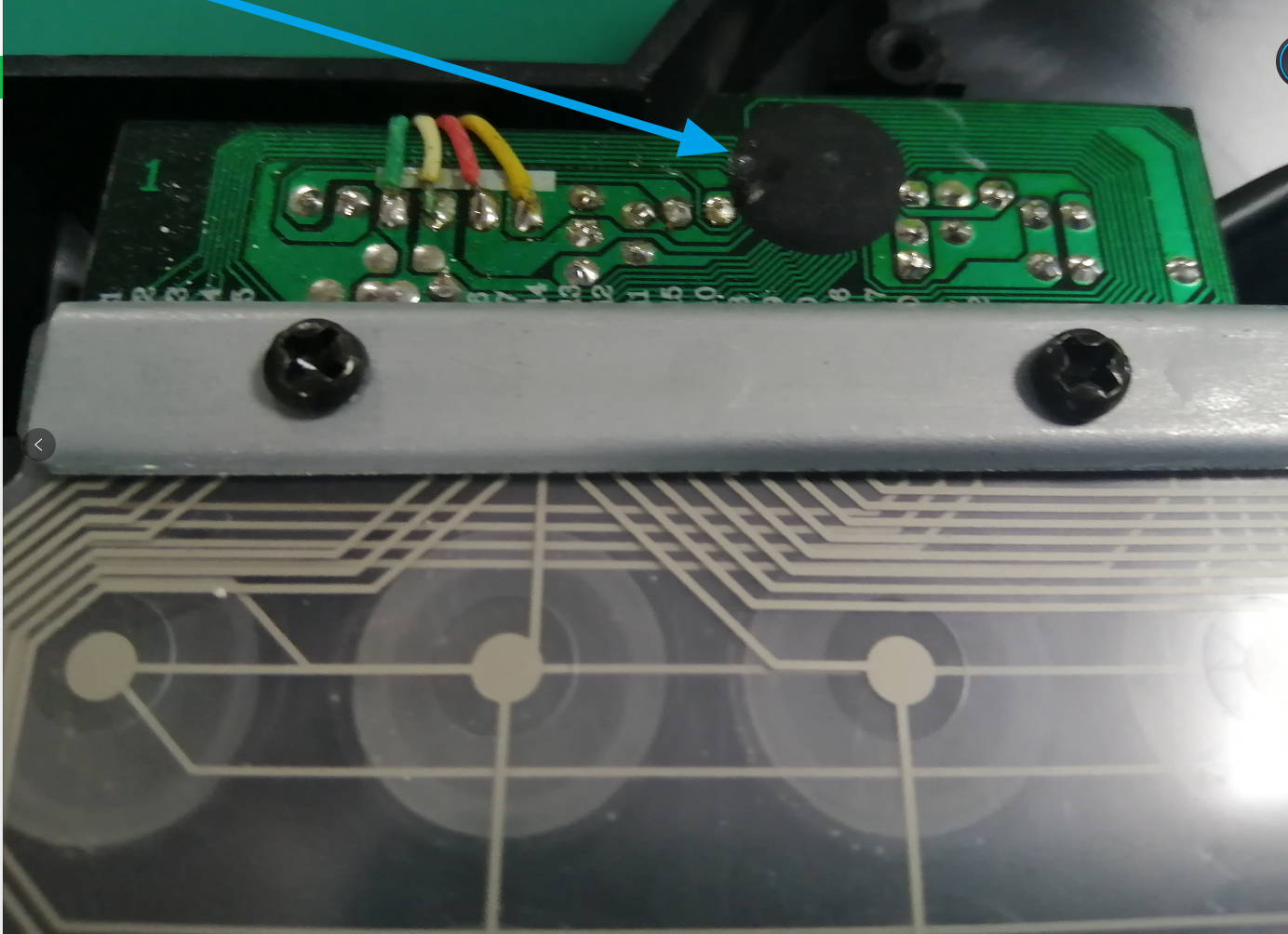

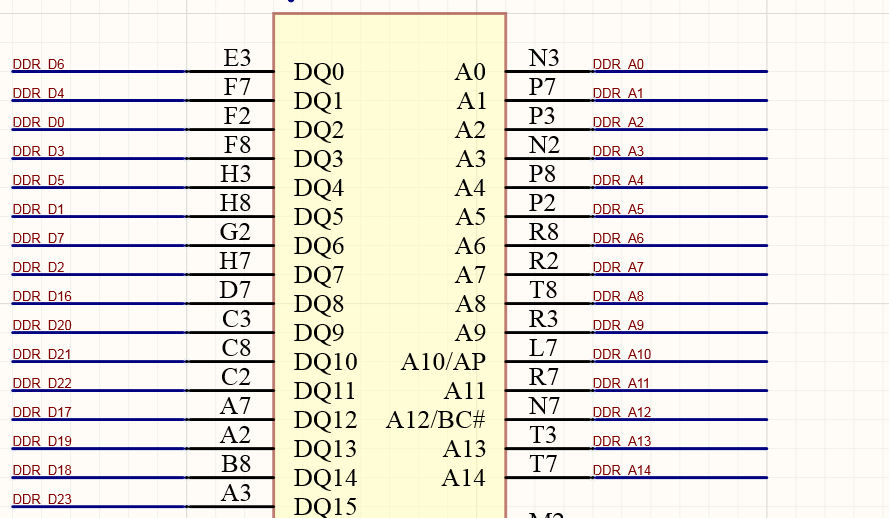

COB封装绑定IC

COB封装即chip On board,就是将裸芯片用导电或非导电胶粘附在互连基板上,然后进行引线键合实现其电气连接。如果裸芯片直接暴露在空气中,易受污染或人为损坏,影响或破坏芯片功能,于是就用胶把芯片和键合引线包封起来。人们也称这种封装形式为软包封。

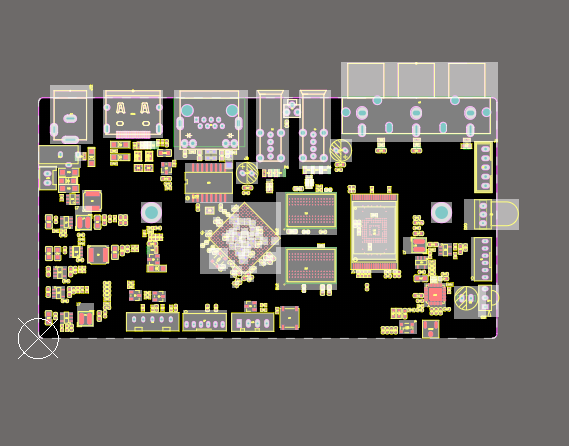

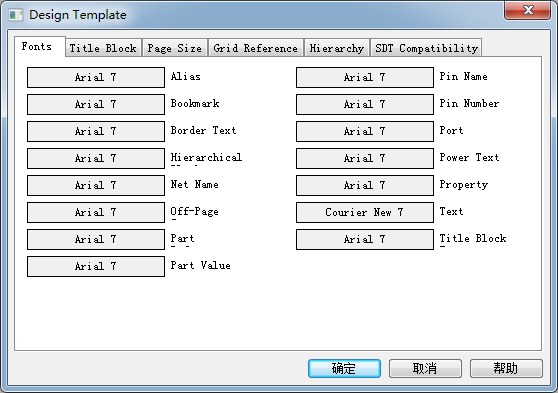

为了提高我们输出文档的模板的一个效率,首先我们的输出文档包括我们的PDf,3D视图,gerber的生产文件,装配文件,等等一系列有关的文件,对于小工程项目的文件的输出,我们一般自己输出文档就够了,然后一个个文件的输出,但是对于我们的大型的项目对策的模板的输出就需要我们使用一个通用的模板进行一个输出,那么这里就需要用到我们Altium Designer 中output job。

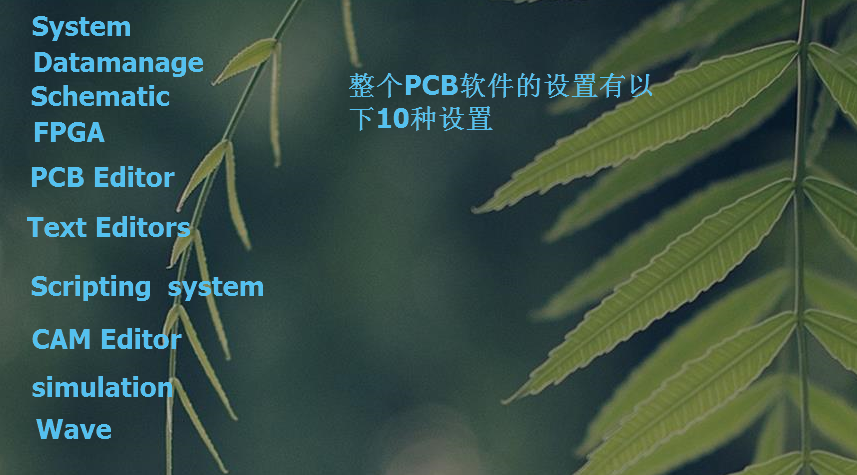

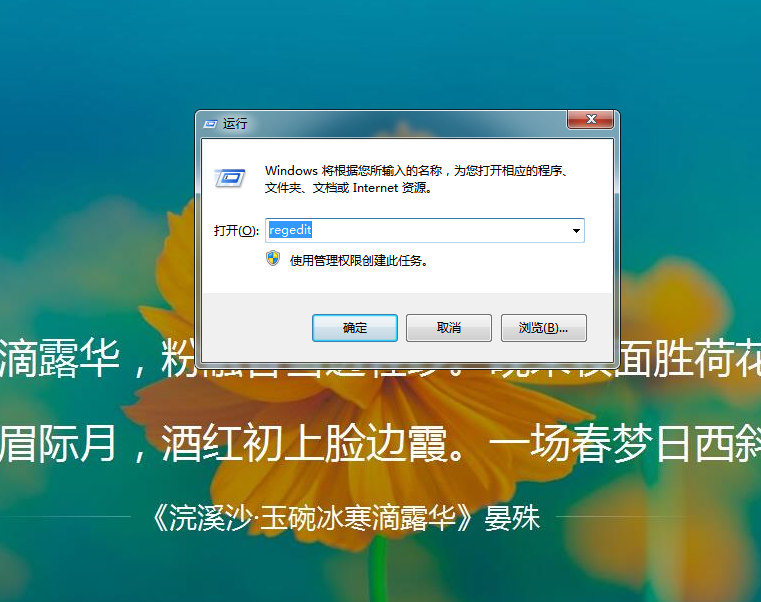

Altium Designer17打开pcb文件卡死(或打开后点击libraries卡死)解决方法

Altium Designer17打开pcb文件卡死(或打开后点击libraries卡死)解决方法

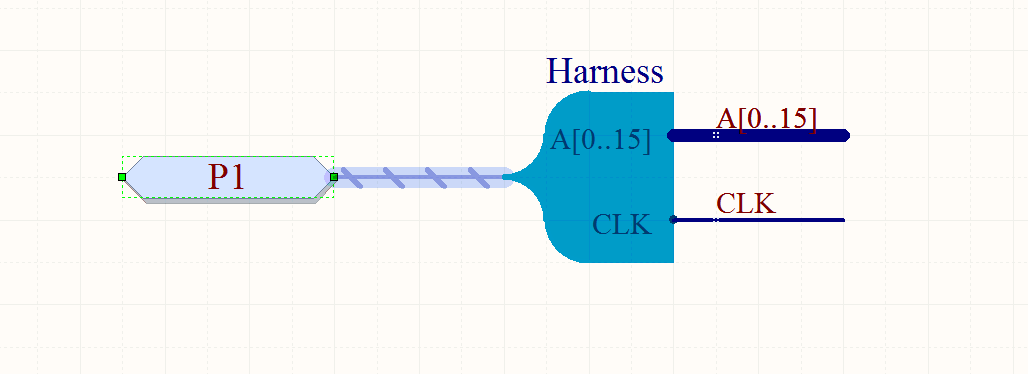

简化原理图线束的使用方法

自Altium Designer6.8之后的版本引入了信号线束(Signal Harnesses)这个概念,并增加了放置、连接功能。信号线束主要用于原理图中连接不同的信号,可以把单条走线和总线汇集在一起并连接到其它信号线束上,这样能简化原理图设计,增强了设计的灵活性和流线性。

扫码关注

扫码关注