- 全部

- 默认排序

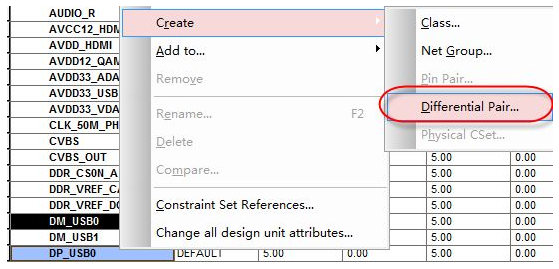

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加一、手动添加差分对:1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然

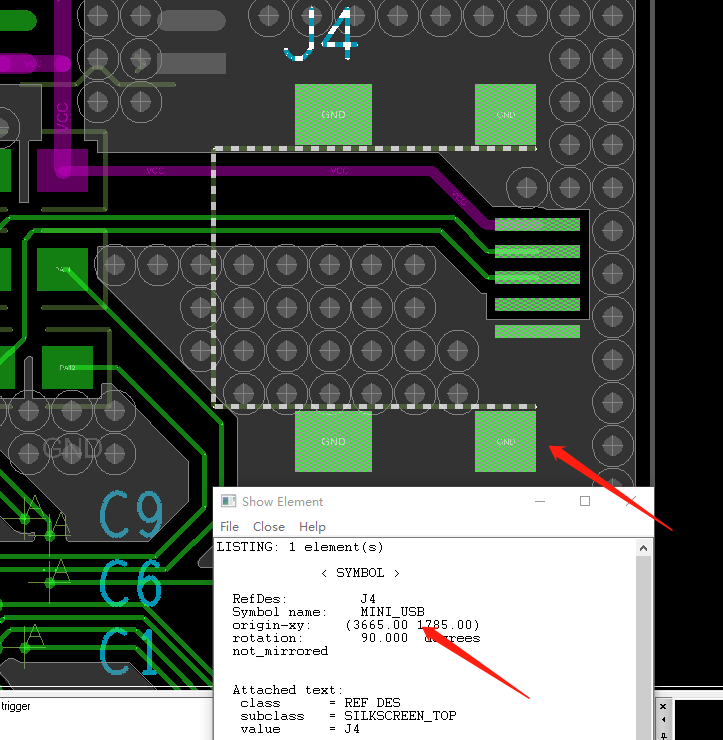

Cadence Allegro单个元器件的PCB封装更新操作在PCB设计中如何对同一种类型的元器件进行封装的更新,有时候会出现这样的情况,出现错误的操作,误删除的其中一个器件的丝印或者是什么的,能否只更新这一个器件呢,其它的不进行更新,当然

Cadence Allegro如何对比两份PCB文件差异在进行PCB设计的时候,有时候会需要对两份PCB文件进行对比,以便核对前后修改后的文件,哪些地方有差异,我们这里讲述一下如何使用Allegro软件对两份PCB文件进行差异化的对比,具体

以下文章来源于Cadence楷登PCB及封装资源中心 ,作者Cadence全球约有三分之二的人口无法获得医学成像服务,其中包括发展中国家,也包括发达国家中医疗资源不足的地区。为此,Butterfly Network 研制了一款基于单个芯片的

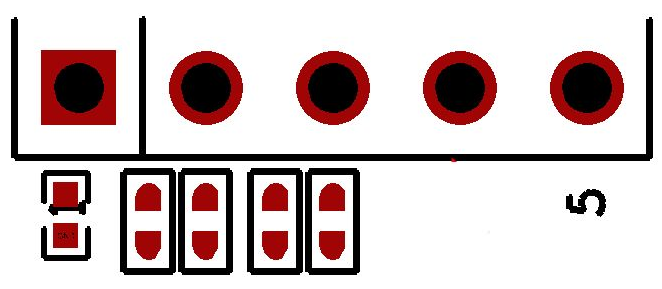

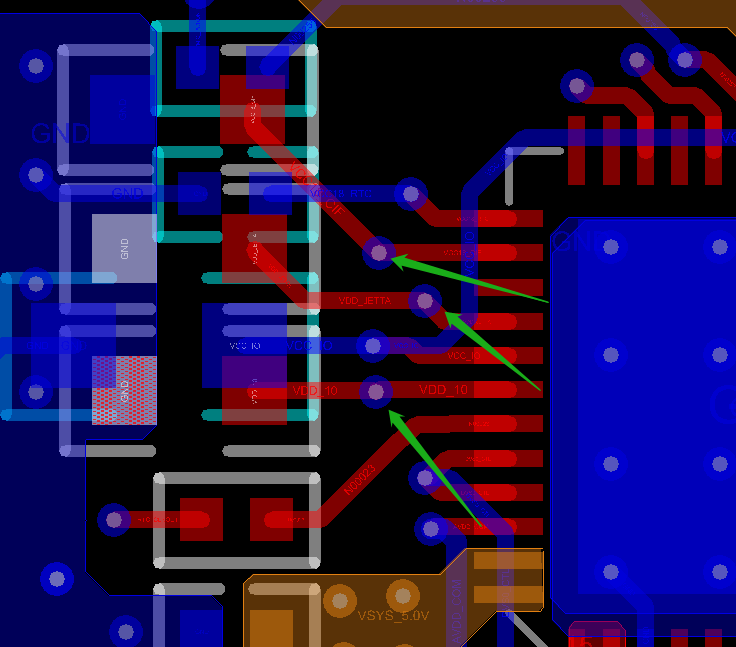

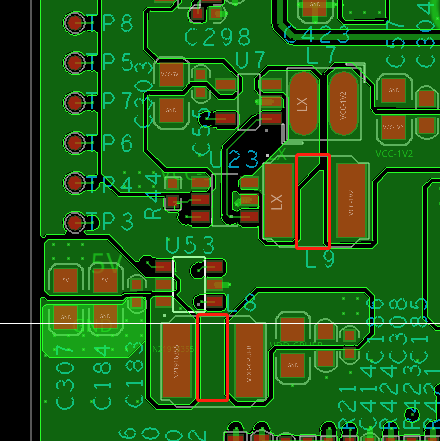

器件摆放时注意主干道尽量一字型摆放2.滤波电容应保持先大后小的原则3.器件摆放尽量中心对齐处理4.DCDC的电源保持单点接地,意思就是输入输出的要统一接入到芯片中心,在芯片中心打散热孔,并开窗处理5.座子要靠近板边摆放,方便后期插拔6.元件

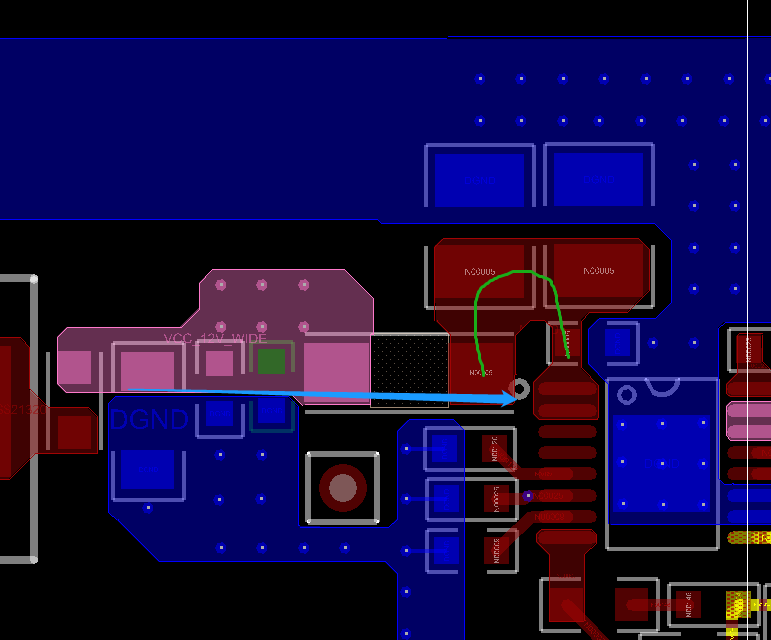

确认一下此处是否满足载流,铜皮尽量不要铺到电容中心,容易造成短路每路都存在一样的问题,后期自己调整一下器件摆放的位置,把铜皮加宽2.器件摆放尽量中心对齐处理3.器件摆放注意方向尽量一致,对齐处理;4.pcb上还存在开路5.座子需要靠近板框外

此处一层连通无需打孔2.注意过孔不要上焊盘3.此处为电源输入,打孔应该打在滤波电容的前面,并且走线加粗4.pcb上还存在飞线5.注意打孔尽量对齐处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

PCB 上存在开路2.DCDC采用单点接地,此处不用打孔3.器件摆放注意对齐处理4.电感所在层的内部需要挖空处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://it

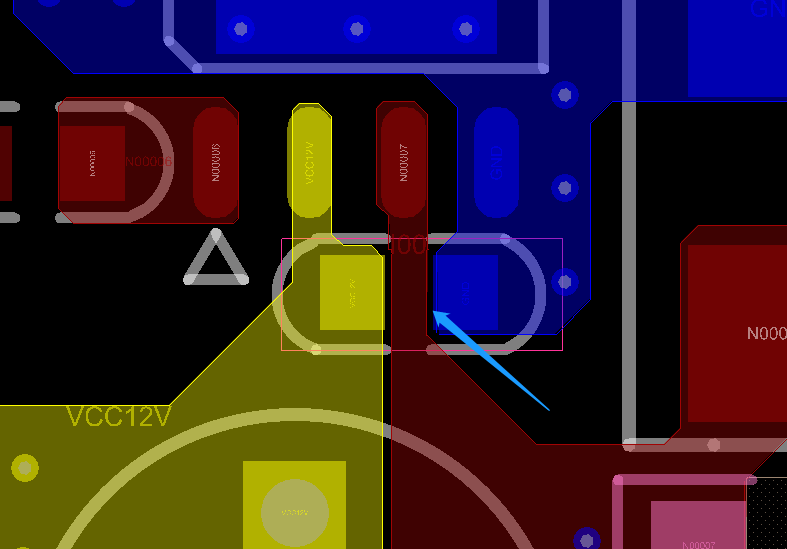

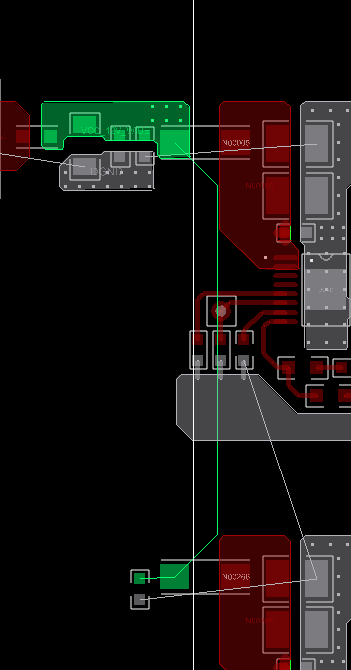

带你干所在层的内部需要挖空处理2.天线做隔层参考,需要挖空第二层3.差分对内等长处理不当,锯齿状凸起高度不能超过线距的两倍4.晶振需要走内差分,并包地,多打地过孔5.注意数据线等长需要满足3W规则6.地址线也需要满足3W规则7.网口差分需要

USB座子焊盘应该放在里边USB2.usb这两根信号需要控90Ohm的阻抗,走差分3.SD卡信号需要等长处理,误差300mil4.232 TX和RX尽量不同层布线,如果同层建议满足5W以上5.走线尽量不要从电阻电容中间穿以上评审报告来源

扫码关注

扫码关注