- 全部

- 默认排序

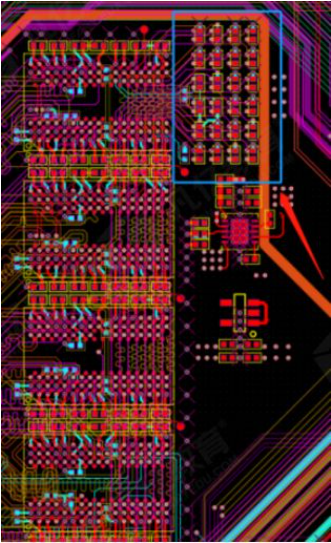

大家如果做过DDR的设计可能会发现在进行多片DDR连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?通常在DDR末端的电阻是为了防止信号反射的,起阻抗匹配的作用,之前我们介绍过另一种防止信号反射的解决措

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在印刷电路板(PCB)设计中,50Ω阻抗值经常被提及,无论是在高速数字信号传输还是射频(RF)电路中,大家好像默认阻抗值都是50Ω,这是为什么?1、历史标准及广泛应用50Ω阻抗值起源于早期的通信和广播电视行业,作为一种广泛接受的标准,它逐渐

在微波电子学中,PCB阻抗匹配可以确保高频微博信号高效从源点传输到负载点,避免信号的反射,进而提升整个PCB系统的能源效益,现在本文将介绍PCB阻抗匹配技术,希望对小伙伴们有所帮助。1、PCB阻抗匹配技术是什么?是指通过调整PCB上传输线的

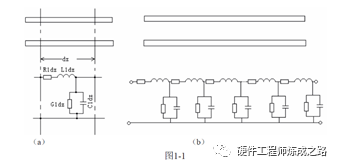

前几天写的关于示波器的文章,提到了探头上面的寄生电容,两个导体并排放置,天然就是一个电容。忽然想到,现如今HDMI 线里面的信号速率到上Ghz,HDMI线也做到了十几米,这么长,等效电容肯定不小啊?这怎么能传呢?信号不都被寄生电容滤波滤没了么?虽说这个时候也能用均匀传输线理论,集总参数模型,分布参数

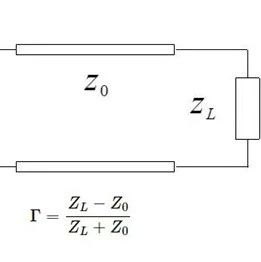

我们为什么需要电路端接?

在电子电路设计中,端接技术是重要的学习内容,因为电路中的阻抗不连续很容易导致信号反射,进而引发信号失真问题,严重影响通信质量,所以端接技术派上用场了。1、信号反射与阻抗不配在电路设计中,端接技术扮演着至关重要的角色。其根本原因在于,电路中的

高速数字电路的阻抗匹配

大家好,我是学电子的小白白。这篇文章我们来聊一聊阻抗匹配,尤其是高速数字电路的阻抗匹配问题。1)什么是阻抗匹配阻抗匹配是指信号源、传输线、负载之间的一种搭配方式。由于实际的信号源都是有内阻的,外面接上传输线、负载时,就不可避免地出现内阻和外部阻抗“分压”的情况。在一个低频电路中,假如信号源的电压为V

本文要点对于射频电路中的阻抗匹配,普遍接受的标准阻抗是50欧姆。50欧姆同轴电缆用于微波发射机、翻译器、调频低功率系统、业余频率系统和双向无线电。要求低衰减的系统的标准阻抗选择是75欧姆。 50欧姆同轴电缆适用于高压、大功率环境传输线阻抗是射频电子学的一个重要方面,因为它极大地影响信号的质量。传输线

扫码关注

扫码关注