- 全部

- 默认排序

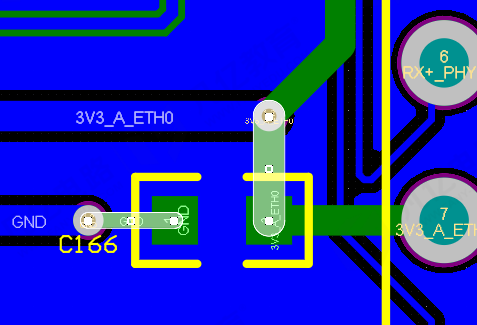

输入电容电源和gnd走线应保持线宽一致变压器除差分外所有走线加粗到20mil以上变压器下方所有层铺铜挖空处理走线注意避免直角锐角时钟走线包地打孔处理过孔间应保持间距交错放置电源应从最后一个器件连接走线间距太近底层大铜皮没有网络,导致gnd网

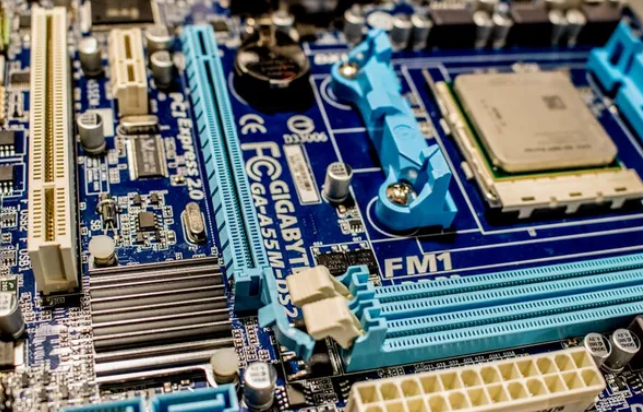

随着电子技术高速发展,许多人开始选择成为电子工程师,在工作时候接受许多项目指派,其中之一是大功率逆变器PCB Layout设计,本文将谈谈这方面的具体注意事项,希望对小伙伴们有所帮助。1、热管理确保IC和其他发热元件底部铺铜,增加散热面积。

在高速PCB设计中,我们经常会看见工程师在电路板上铺铜,确保电路板的性能是稳定且可靠的,但有没有更深的原因?一起来看看吧!1、EMC屏蔽与防护大面积的地(GND)或电源(VCC/VDD)铺铜可以有效屏蔽外部电磁干扰,保护内部信号不受影响。特

请教各位,如下图所示,明明设置了十字连接,并且更新了铜皮,可是,铜皮和pin并没有连接上,那位知道啥原因?

图示的线段位于这个层( Board Geometry\Outline ),红色箭头部分,要做V形切割,有如下两个疑问:1、如何将需要切割的线段(红色箭头处)表示在Art文件里?2、切割角度和深度如何表示在Art文件里?

当对allegro软件PCB层叠结构进行设置的时候,某一层可以设置为plane或者conduct,平面层和走线层。但是我发现无论是设置成plane还是conduct,这一层都可以走线,手动铺铜皮,edit-split creat这样去灌铜进行铜皮分割。既然这样,那么设置层的时候,plane和cond

如标题所述:Altiumdesigner17版怎么来设置铺铜到板框和与走线间的不同距离设置?同一个网络铺铜: 要求1:铺铜到板框的距离0.15mm要求2:铺铜到其它走线的距离是0.3mm要怎么设置啊(最好有祥细的图文步骤),求各位大神支招,感激不尽。

扫码关注

扫码关注