- 全部

- 默认排序

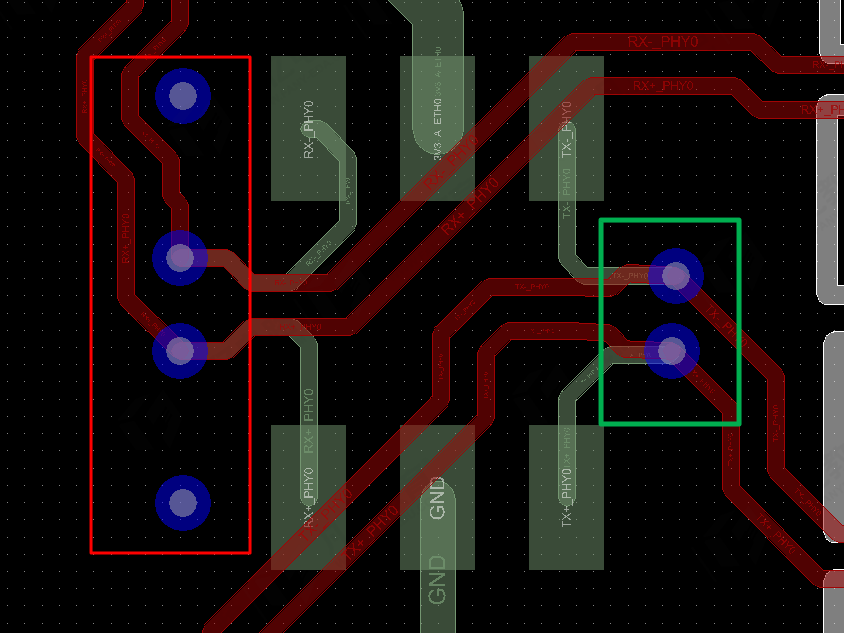

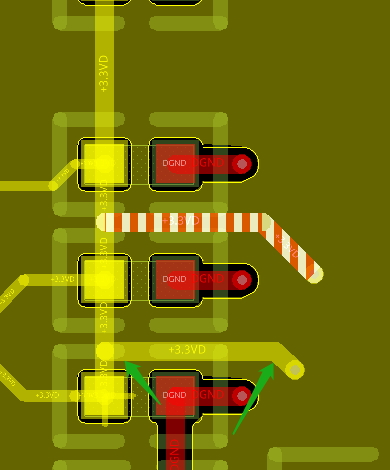

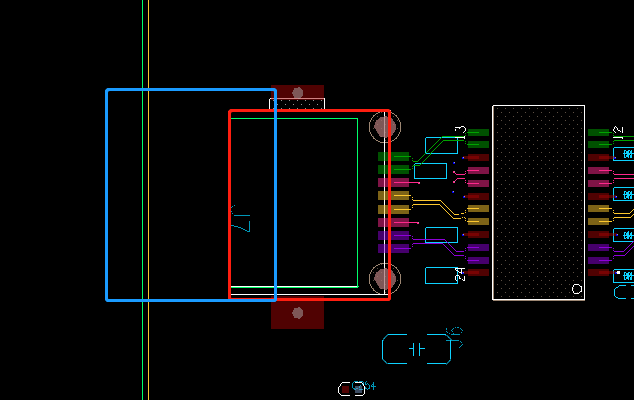

1.差分换层旁边需要打回流地过孔。2.差分对内等长不符合规范3.差分对走线出焊盘过长距离不耦合,应按规范中出线4.变压器所有走线包括电源加粗到20mil以上线宽5.布线不满足3w间距要求6.差分网络没有连通7.焊盘出线应从焊盘中心出线,平行

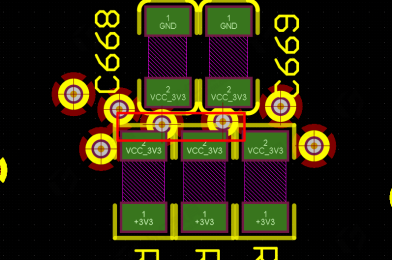

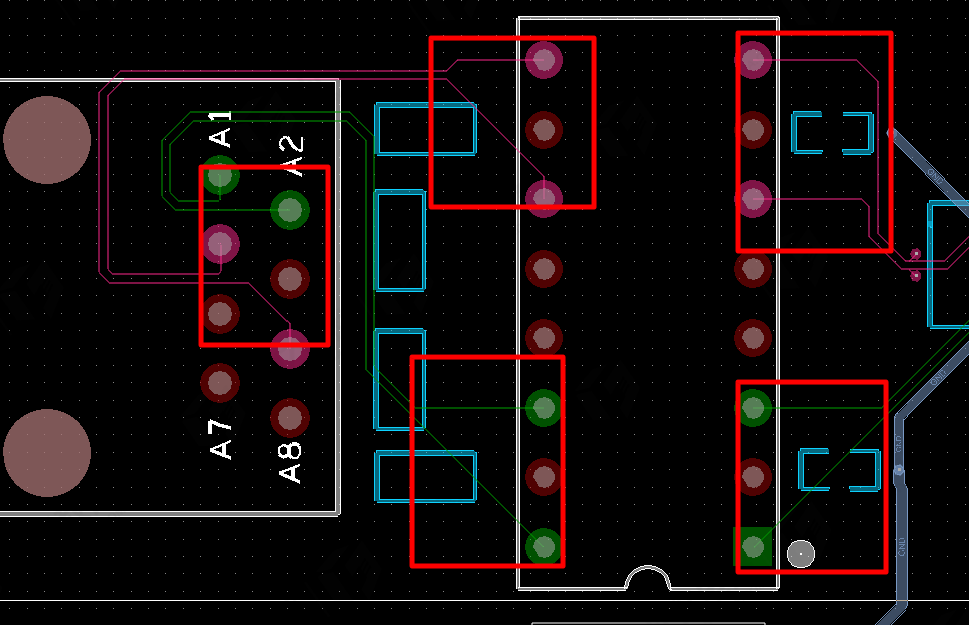

1.过孔上焊盘 2.多余过孔、线头造成天线报错 3.封装极性标识放置层错误 4.过孔应该打到最后一个电容后方,经过电容在连接到地铜5.晶振应走类查分形式 6.电源焊盘和铜皮连接处需要加宽 7、多处孤岛铜皮、尖岬铜皮、锐角、直角铜皮 8、需

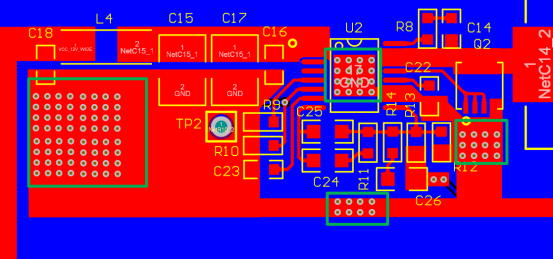

1、要求单点接地,一路dcdc的地网络全部连接到芯片下方打孔接地 2、电感下方应该所有层挖空处理 3、铺铜避免直角锐角 4、电源接口应靠近板框一端伸出板框方便插拔 5、电源铜皮不够宽 6、底层未连接电源的多余过孔导致天线报错以上评审报告来源

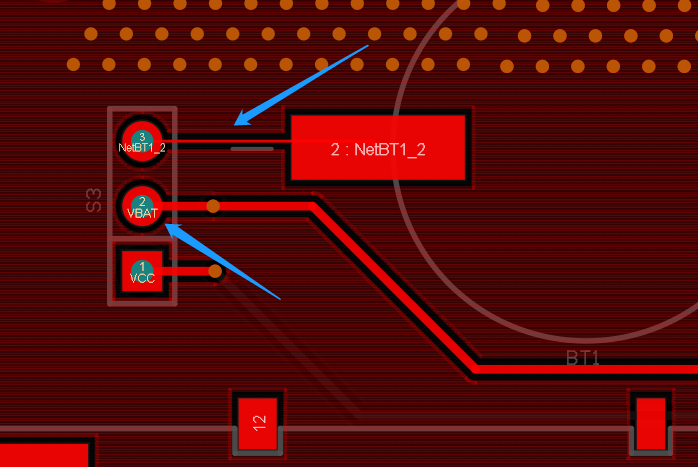

此处两个过孔不满足载流2.电感所在层的内部需要挖空处理3.反馈线宽尽量保持一致4.电源需要再底层铺铜进行连通,地网络同样的处理方法5.注意走需要优化一下,要连接到焊盘中心以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

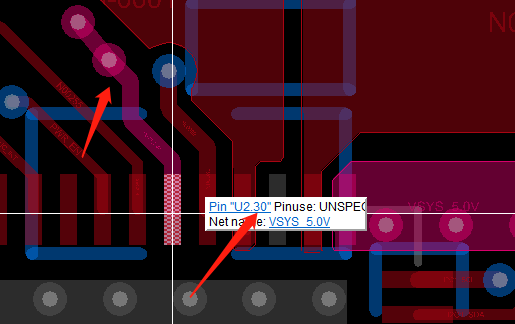

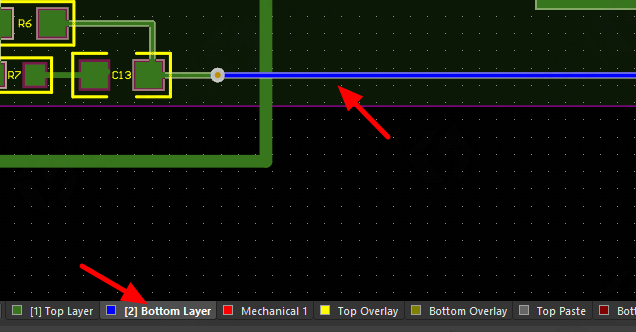

注意此处扇孔可以直接打在走线中间,这样拉出去形成了直角:注意个别过孔的间距,不要割裂了铜皮:注意数据组跟地址控制时钟组之间用GND走线隔开:再有空间的情况下 ,自己处理下。等长注意GAP尽量大于等于3W长度:优化处理下。其他的等长误差没什么

1.底层没有铺地铜,导致多处地网路飞线没处理2.多处铺铜没有网络,多处飞线没有连接3.dcdc需要单点接地,地网络没有打孔,应在芯片下方打孔和大地铜连接4.电源没有连接,多处过孔没有网络5.地网络没有连接,6.铺铜、走线避免直角锐角7.走线

1.差分出焊盘后应就近耦合,尽量保持长度相等2.差分换层应该从过孔中间连出,旁边打上两个回流孔3. 走线多处锐角,应该避免锐角直角4.走线应该尽量短不要绕,时钟走线需要包地处理5.差分走线长距离不耦合6.走线直接连接就可以,删除多余走线7.

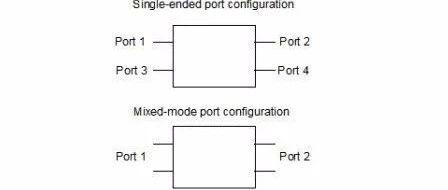

单端S参数转差分S参数

在射频领域,一般都是单端器件,走单端线;在数字硬件,走速率高的线,一般都是差分线。而且那些高速串口信号传输速率越来越高,10GSPS已经变得很寻常。而当你布线的时候,可能不得不打个过孔,从TOP面穿到BOTTOM面;可能还需要差分线尺寸,以能进入FPGA区域;又或者你需要把线走成弯弯曲曲的,以满足等

RJ45的座子要靠近板框放置2.注意差分走线要尽量耦合3.网口除差分信号外,其他的都需要加粗到20mil,器件靠近管脚放置4.晶振需要包地处理5.注意过孔不要上焊盘,地网络就近打孔,缩短回流路劲6.差分对内等长存在误差报错7.TX和RX要添

电源走线需要加粗,满足载流2.注意焊盘出线规范3.晶振需要包地处理,并打上地过孔,晶振下面不要走线4.走线与焊盘同宽,拉出焊盘在进行加粗处理5.232的升压电容走线需要加粗处理6.输出滤波电容先大后小摆放7.注意USB2.0有一对差分,对内

扫码关注

扫码关注