- 全部

- 默认排序

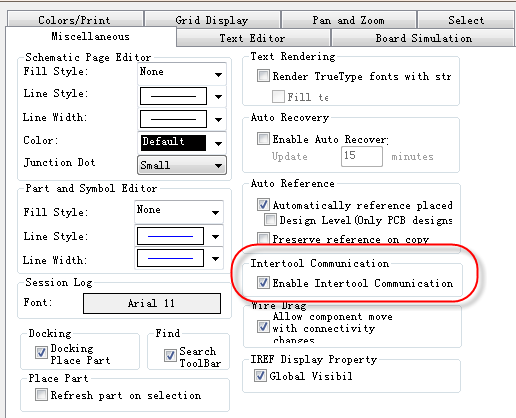

在前面的问答中,我们分别详细讲述了第一方网表与第三方网表的输出方法与导入方法,这两种导入方法有什么区别与联系呢,是不是都可以呢?这里呢,我们讲解一下第一方网表与第三方网表的区别与联系,具体如下:首先,如果是在Allegro软件中导入的是第一方网表,是可以进行同步操作的,导入的第三方网表,是不可以进行不同操作的,第一方网表导入的时候,需要进行同步操作都设置在原理图设置下,如图6-34所示,将第二个选项勾上即可; 图6-34 同步操作设置示意图其次,Allegro软件的第一方网

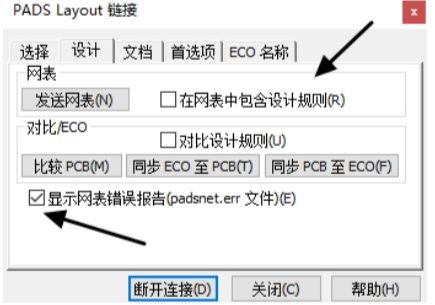

原理图设计完成后,需要将原理图中的设计内容导入到PCB中,以方便后续PCB设计工作,PADS Logic与layout进行同步过程,可以完成。1)执行菜单栏命令“工具”→“PADS Layout链接”或者点击快工具栏的快捷键,点击完成会弹出

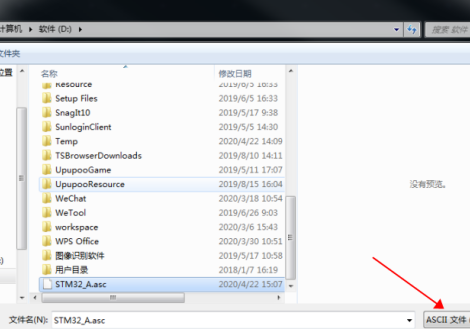

PADS Layout导入网表,即将原理图与PCB进行同步,具体步骤可参考“4.6.1 PADS Logic与layout同步操作”内容。除了导入Logic原理图文件,还可将Orcad原理图导出的ASC文件导入到Layout内。1)执行菜单

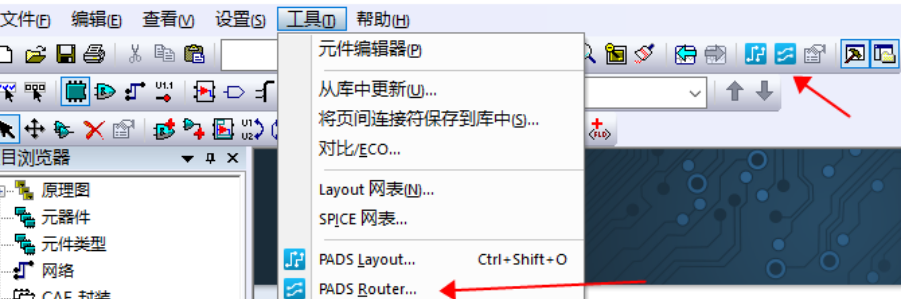

在Logic组件中,既可以和Layout组件同步设计,也可以与Router组件同步,在Logic组件中执行“工具-Pads Router”,可将Logic与Router进行同步,执行此操作时建议不要打开多个设计,以免系统同步错文件。如图6-

很多电子工程师在设计时域电路中,总会遇见很多很多问题,其中之一就是多时域设计中如何处理信号跨时域?这个问题曾劝退很多萌新,今天我们将回答这个问题。不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下

时钟发生器在计算机中起着非常重要的作用,主要包括以下几个方面:芯片同步:时钟发生器产生稳定的时钟信号,用于对计算机内部各个芯片的工作进行同步和时序控制,确保它们按照正确的顺序和速率进行操作。CPU同步:时钟信号被用来控制中央处理器(CPU)

扫码关注

扫码关注