- 全部

- 默认排序

电子设计中电容的选择

在电子设计芯片的电源输入端一般都会加一颗贴片电容,比如单片机的电源输入端、运放的电源输入端等,电容的个数与电源的通道数一致。一般这个电容选用0.1uF的。如下图所示是AT24C02电源引脚所接的电容。 单片机或者是通信芯片等需要用到晶振的芯片,在设计无源晶振电路时,用两个电容和晶振构成震荡起振电路为芯片提供时钟频率。一般这个电容的选择范围为(15-30)pF,有的芯片会在数据手册上写明不同晶振下该选用多大的电容。 电容具有储能作用,通过设计不同的串联电阻,可以改变电容的充放电速度,也就起到了

mcu电路设计问题总结

单片机一直处在复位状态时根本无法工作。出现这样的原因是由于RST引脚内含三极管,即便在截止状态时也会有少量截止电流,当R取的非常大时,微弱的截止电流通过就产生了高电平。 二、LED串联电阻的计算问题 通常红色贴片LED:电压1.6V-2.4V,电流2-20mA,在2-5mA亮度有所变化,5mA以上亮度基本无变化。 三、端口出现不够用的情况 这时可以借助扩展芯片来实现,比如三八译码器74HC138来拓展 四、滤波电容 滤波电容分为高频滤波电容和低频滤波电容。

电路设计防静电原理解析

一、静电放电波形和能量频谱 静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前辈电路设计了很多静电放电模型。 常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规

CH340芯片通过USB转换出来的TTL串口输出和输入电压是根据芯片供电电压是自适应的。也即,如果芯片是5V供电,那么串口输出和采样都是5V;如果是3.3V供电,那么标准就成了3.3V,因此在实际使用的时候,电路设计串口连接到的对端设备需要注意电压匹配的问题。其中在5V供电模式下,是可以与3.3V系统兼容的,反过来则不可以,如果CH340是3.3V供电,那么不可以接5V系统,会损坏芯片。另外如果对端是1.8V系统,那么是不能与CH340的3.3V模式兼容的,此时输出和采样会出错。最好加一些器件来

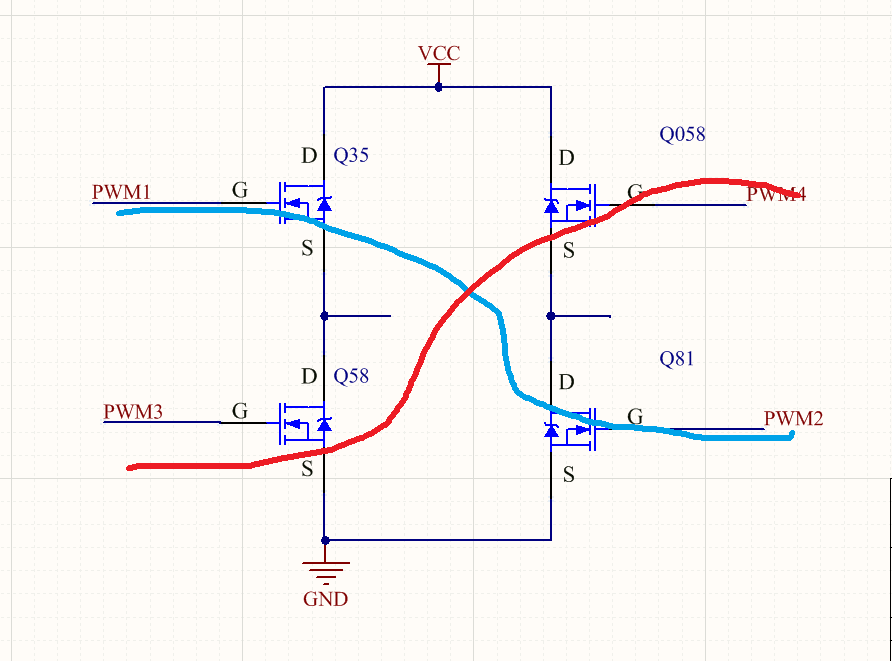

电路设计之过压保护电路

电路设计常用直流电源 在很多的电子产品设计中,电源部分是极为重要的,也是很容易损坏的。一方面是输入的电源极性错误,这个我们之前的文章,也介绍了一部分防止极性发生错误的电路。另外一方面是输入的电压过高。下面我们主要讨论如何简单、可靠的解决电路设计这个问题。 比如在电子器件电源前端的电源不稳定,如汽车电瓶在汽车启动时,会产生很大的浪涌电压。对于此类过压电源的保护,一般采用TVS管去保护。一般应保证TVS管应工作在后端电源芯片器件的正常电压VCC以上,最大工作电压Vmax以下。 TVS管应用电路

RF电路设计一些心得体会

当我们设计上接触一个全新的RF芯片,要求我们能够快速的了解这颗芯片RF部分电路的性能指标及对外围器件的要求,还要快速的做好这部分的电路设计工作时,我们最首要需做的就是仔细阅读并理解芯片规格书和参考板的设计及注意事项,这对于我们第一版设计的成败起到很关键的作用,特别是有些RF芯片和RF外围的某些特定的RF器件(如外加PA LNA BPF等)配合这一块尤为重要。走线及阻抗控制的好坏直接会影响到整个RF部分的后期调试指标的好坏,所以说电路设计初期对于RF芯片的EVB板的设计要求一定要参考,这样才能事半

什么是集成电路设计

集成电路设计,根据当前集成电路的集成规模,亦可称之为超大规模集成电路设计,是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计通常是以“模块”作为设计的单位的。例如,对于多位全加器来说,其次级模块是一位的加法器,而加法器又是由下一级的与门、非门模块构成,与、非门最终可以分解为更低抽象级的CMOS器件。下面就让我们进一步的了解集成电路设计的相关知识。 集成电路设计介绍 集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。芯片硬件设计包括: 1

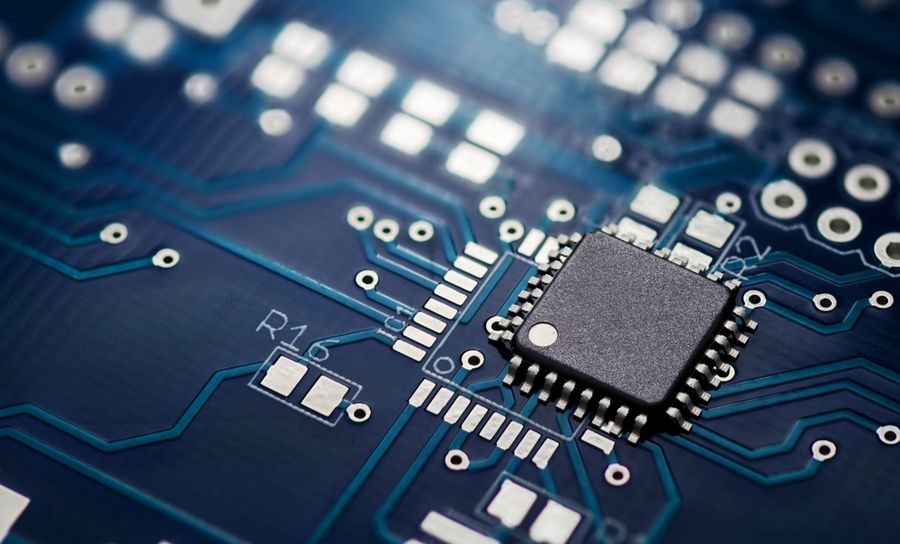

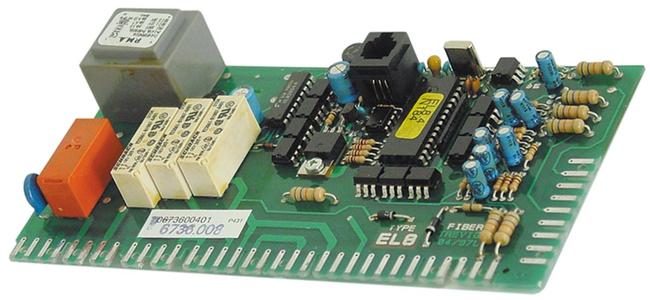

单片机硬件系统电路设计

单片机硬件系统的硬件电路设计包含两部分内容:一是系统扩展,即单片机内部的功能单元,如ROM、RAM、I/O、定时器/计数器、中断系统等不能满足应用系统的要求时,必须在片外进行扩展,选择适当的芯片,设计相应的电路。二是系统的配置,即按照系统功能要求配置外围设备,如键盘、显示器、打印机、A/D、D/A转换器等,要设计合适的接口电路。 系统的扩展和配置应遵循以下原则: 1、尽可能选择典型电路,并符合单片机硬件系统常规用法。为硬件系统的标准化、模块化打下良好的基础。 2、系统扩展与外围设备的配置水

电路设计dummy的作用

在电路设计中dummy的作用是: 1. 保证电路可制造性,防止芯片在制造过程中由于曝光过渡或不足而导致的蚀刻失败:如在tapeout的时候会检查芯片的density,插入dummy metal、dummy poly、dummy diff等; 2. 避免由于光刻过程中光的反射与衍射而影响到关键元器件物理图形的精度进又而影响其size:如在模拟电路的电阻、电容阵列外围加上dummy res和dummy cap等,以及关键MOS附近加dummy MOS等;

扫码关注

扫码关注