- 全部

- 默认排序

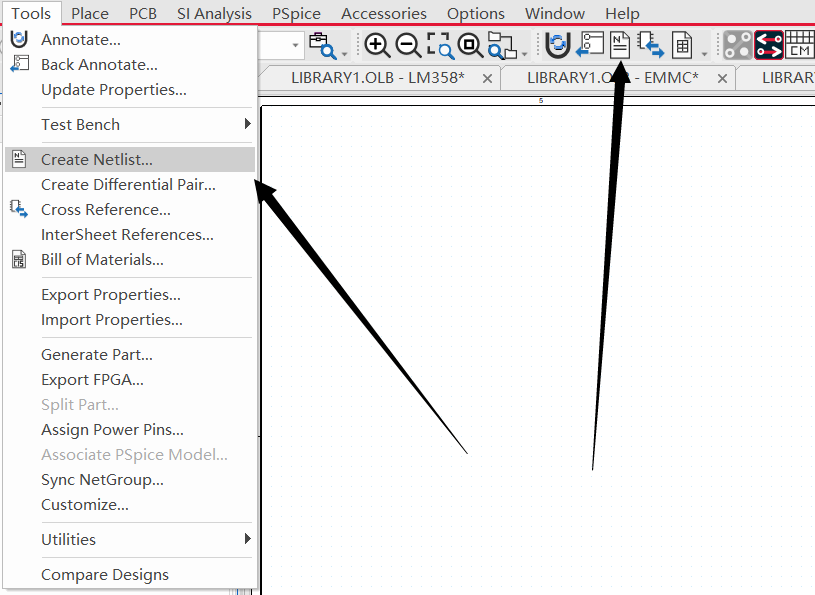

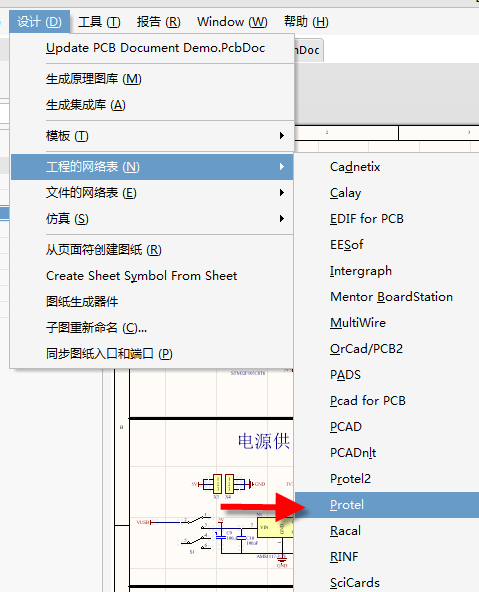

答:原理图检查,检查是否有单端网络、连接错误、没有指定封装等设计问题→原理图输出网表以及网表检查→检查封装库,没有封装库的,匹配原理图,新建封装库→导入原理图网表,将所有器件导入到PCB中→核对产品结构图纸,定位好结构器件→PCB版图布局→布局优化以及布线规划→层叠设计以及整个PCB图的设计规则添加→PCB版图布线→PCB版图电源分割与处理→布线优化→生产文件(Gerber)的输出,凡亿教育推出的有全流程的PCB设计实战视频教学,有需求的可以联系作者购买学习。

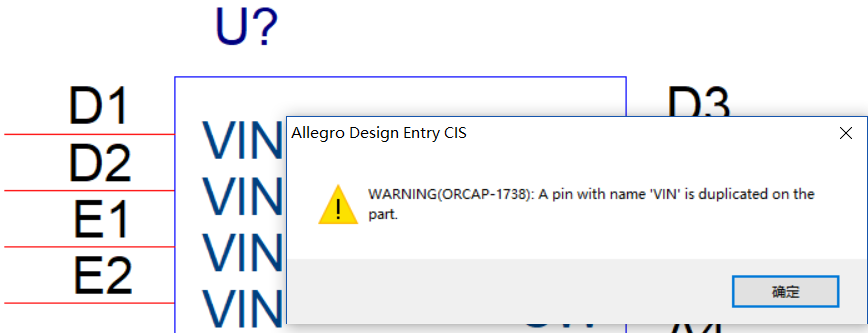

答:在绘制原理图库,会出现一些管脚名称是一样的,一般是电源管脚或者是空管脚,当名称重复的时候,保存原理图库的时候,会弹出如图2-78所示的警告,提示有重复的名称,后面输出Allegro网表的时候,会报错。对于这种情况,我们做如下处理: 图2-78 原理图库管脚名称相同警告示意图Ø 电源管脚名称一致的,我们将电源管脚的属性改为power属性,这样系统就会允许管脚名称是一致的,不会报警告,如图2-79所示; 图2-79 电源管脚属性示意图Ø

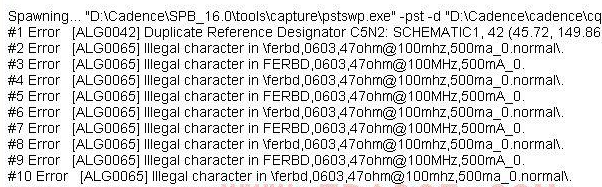

答:orcad当前设计中,所用到库在原理图页面下方的Design Cathe里,在绘制原理图时,可能很多部分是从别的原理图拷贝而来,所以Design Cathe中就会存在一些非法字符,从而影响网表的输出,我们就需要将Design Cathe中的非法字符消除,消除的步骤如下:第一步,点击菜单File→New Library,新建一个库在当前设计的路径下,注意保存的时候不要在路径上出现非法字符,如含有括号、百分号等;第二步,在Design Cathe中找到库路径中含有非法字符的那个库文件,选中库文件

扫码关注

扫码关注