- 全部

- 默认排序

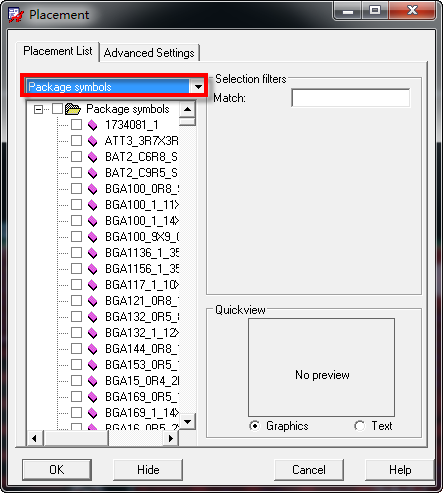

答:一般,批量添加封装到PCB板上有以下方法:首先,在导完网表后,可点击Place-Quickplce…选项,然后在弹出的选项里按图示参数勾选,选好后可点击Place即可将原理图中指定好的器件批量添加到PCB中,如图4-113所示:

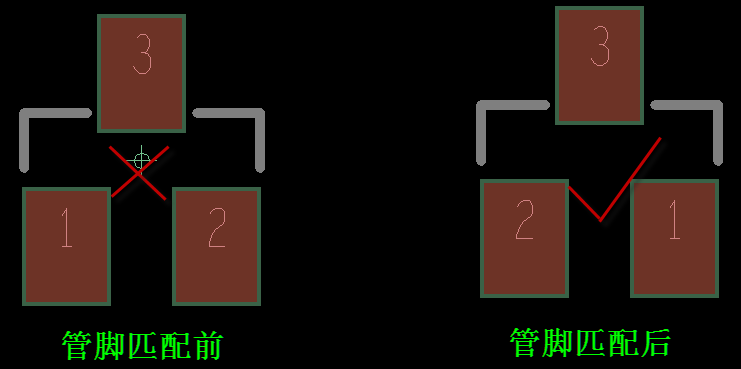

答:在制作封装时,经常会碰到要进行封装管脚匹配,特别是3极管类型封装,特别容易将管脚排序做错。以下给大家介绍三极管管脚排序的方法:第一步,打开原理图,找到对应的器件,查看器件的管脚排序,如下图,分析图示可知,1脚为E极,2脚为B极,3脚为C极,如图4-119所示

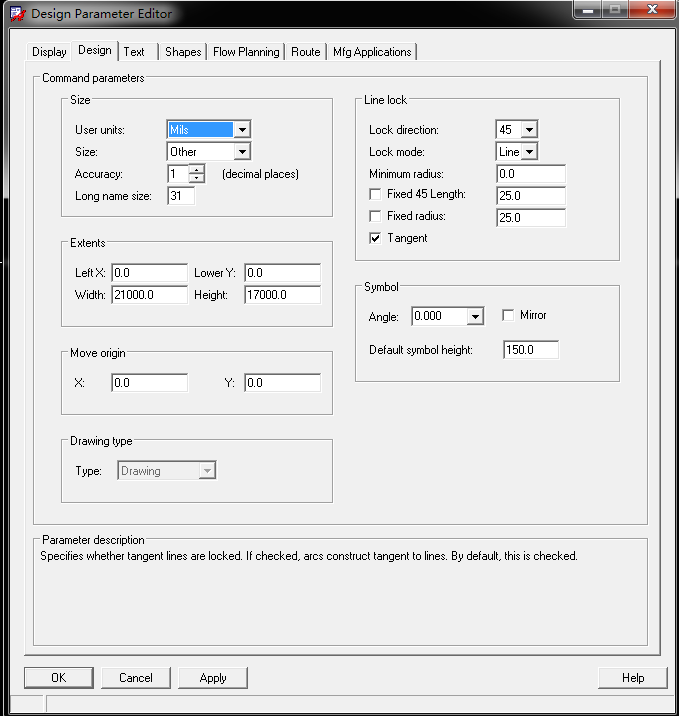

答:按照第5.22问的方法,进入整板的参数设置界面之后,在Display右边选中第二项,就是Design面板,如图5-52所示,在这个Design面板,对设计的一些参数进行设置,具体每一个命令详细的含义,如下所示:

答:在使用Allegro软件进行PCB设计的时候,经常会要遇到这样的问题,在这个软件中,怎么去快速的找到一个元器件,有哪些方法可以使用,所以呢,这里我们讲解一下,在Allegro软件中快速定位元器件的几种方法,具体如下:

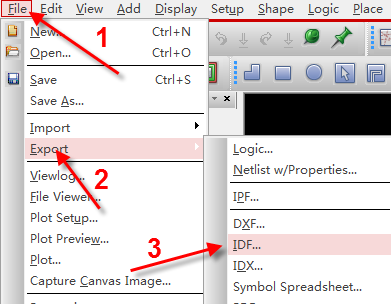

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

答:在进行PCB设计时,完成布局操作之后,为了更好的核对结构,除了导出2D的DXF文件之外,还需要导出3D文件,导入到PROE软件中进行对比,这样更能非常显著的看出结构是否有问题,具体导出的方法如下所示:

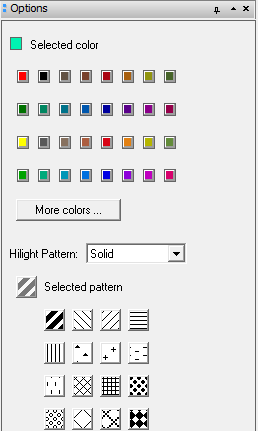

答:高亮显示命令,也就是Assign Color命令。在Allegro软件进行PCB设计的时候,是应用非常广泛的命令,如图5-76所示。这里我我们详细介绍一下,高亮显示的使用方法以及在Options参数面板的设置,具体如下:

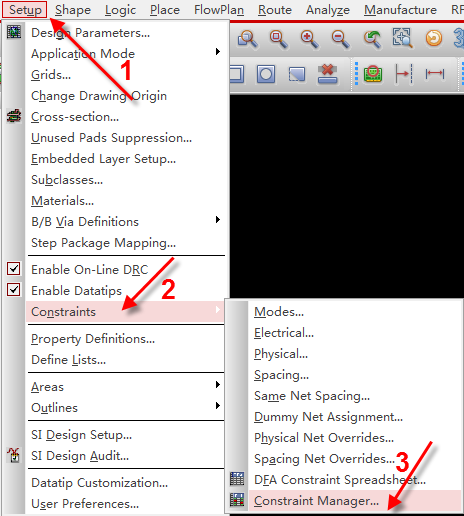

答:我们在设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。一般情况下如果信号是从一个点传输到另一个点,中间没有任何的串阻、串容,这个绝对传输延迟的方法还是非常有效而却直观的。具体在PCB中设置绝对传输延迟的方法如下所示:

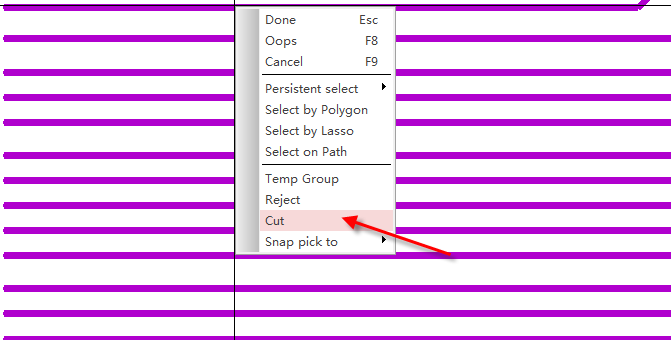

答:CUT功能,就是切除一整段线中间一部分的功能,是删除功能下所附属的一个功能,可以CUT的对象可以是电气走线,如cline,也可以说非电气走线,如line,操作的方法都是一致的。这里以CUT一段Cline为例,讲解一下CUT功能的使用

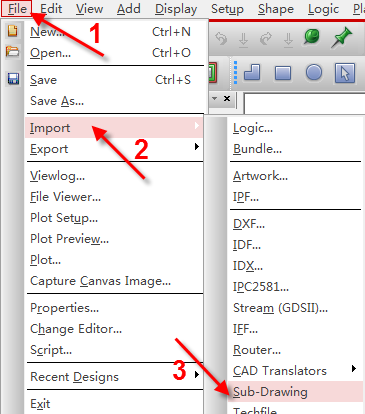

答:在前面的问答中我们讲解了Team Design功能的详细使用方法,除了这种方法可以进行协同设计以外,这样是最高效的方法,Sub-drawing功能也是可以的,简单的说,Sub-drawing就是从别的PCB文件拷贝器件或者走线到当前的PCB文件中,而copy命令也是复制功能,但是只能应用于同一个PCB文件中,这个是二者最大的区别,以下我们讲解一下,Sub-drawing功能的具体的应用方法,操作如下:

扫码关注

扫码关注