- 全部

- 默认排序

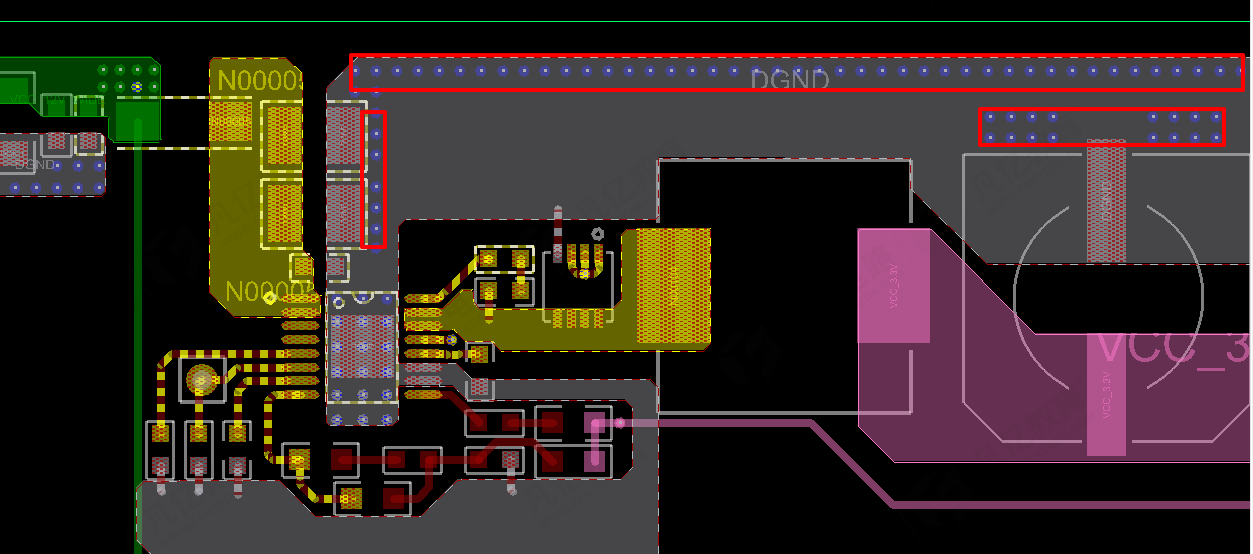

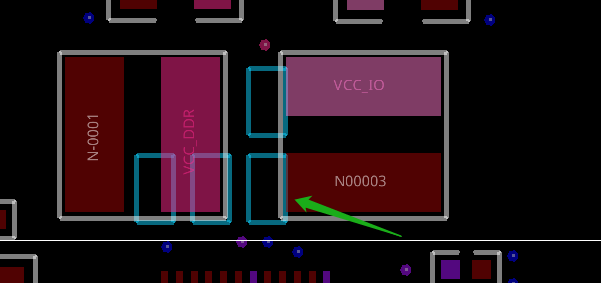

布局没什么问题,注意电感内部需要挖空处理的:此处也是一致的问题,自己去放置禁止布线区域:注意板上的走线都一直线宽,除了特殊信号的:注意打孔注意对齐等间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PC

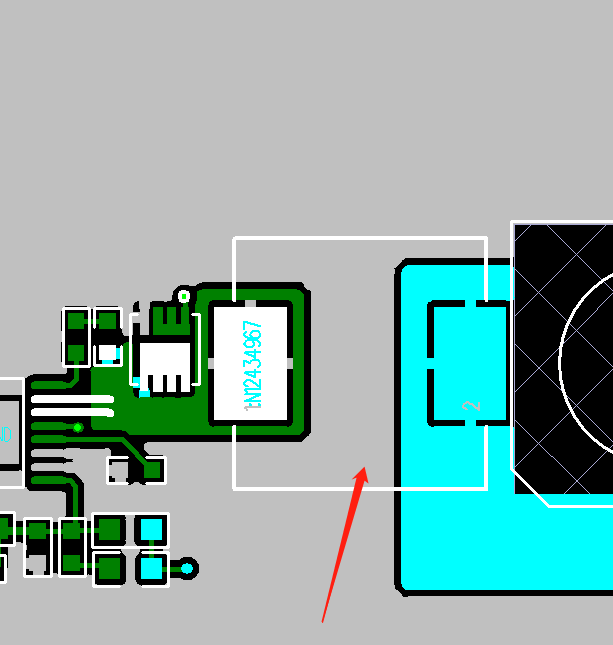

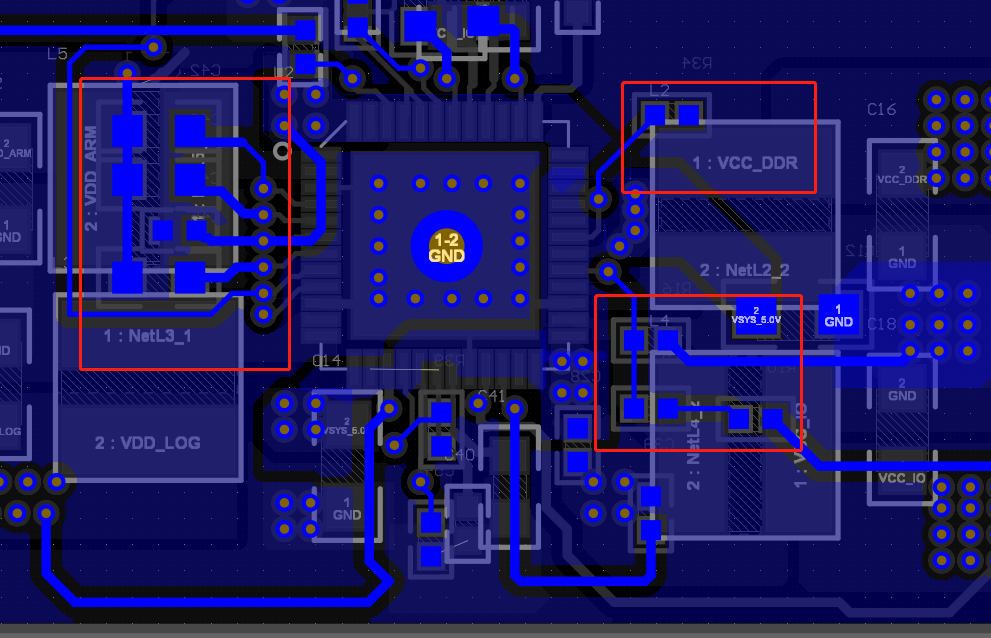

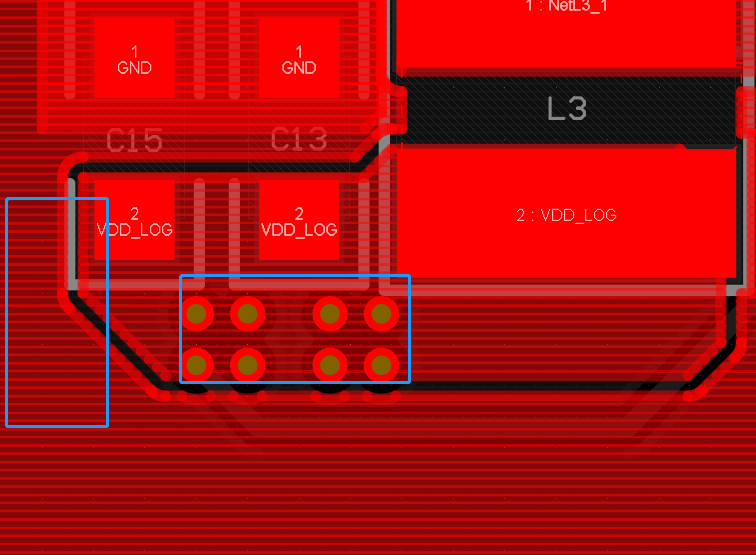

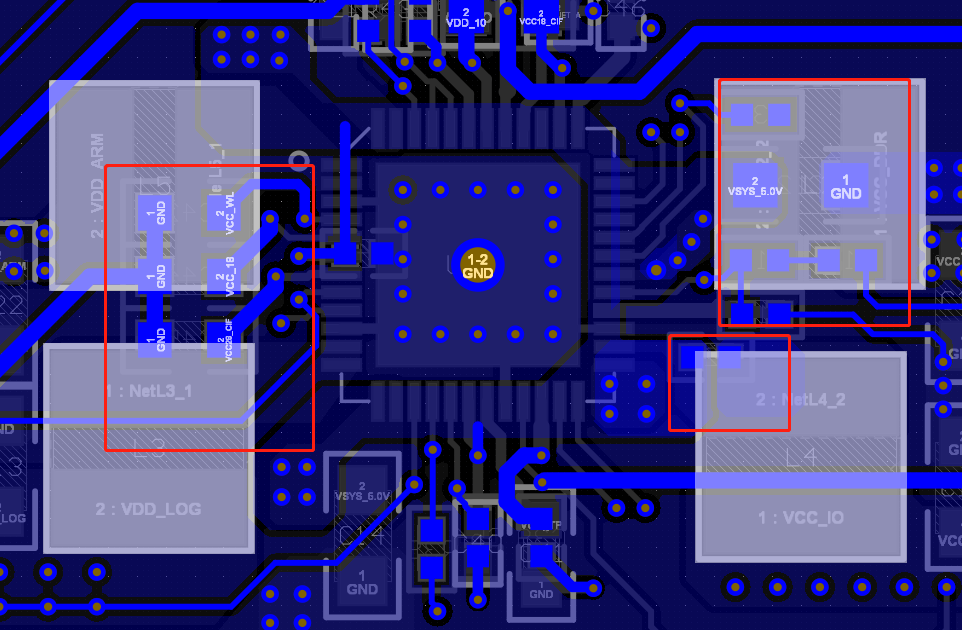

1.dcdc需要单点接地,gnd网络需要连接到一起在芯片下打孔。2.相邻电感不能平行摆放,需要朝不同方向垂直放置。3.下面一路dcdc电源输入需要加粗,加宽载流从第一个器件输入。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了

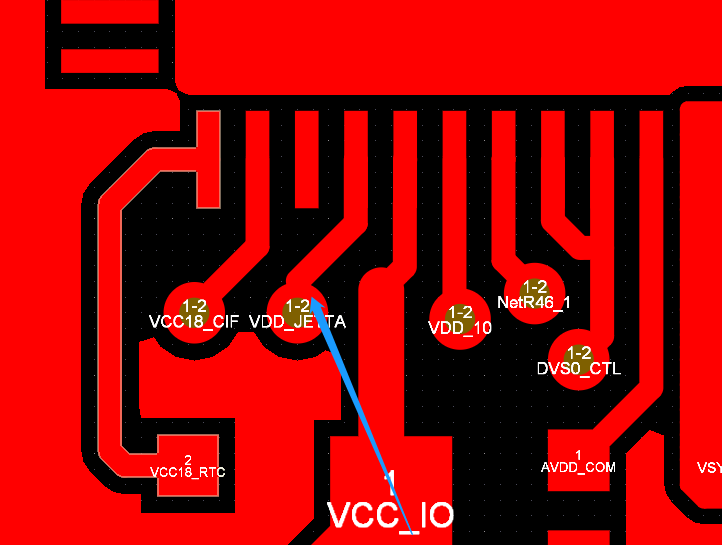

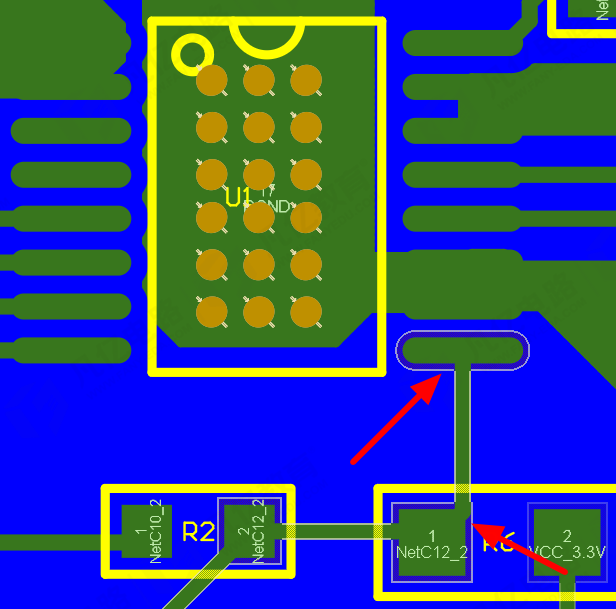

反馈线只用走10mil即可2.输出打孔要打在最后一个电容后面,反馈走线即可,不用铺铜输出打孔都需要再调整一下3.此处存在drc,短路了4.此处不满足载流,建议铺铜处理5.此处反馈器件要靠近管脚放置6.管脚滤波电容需要靠近管脚放置,保证一个管

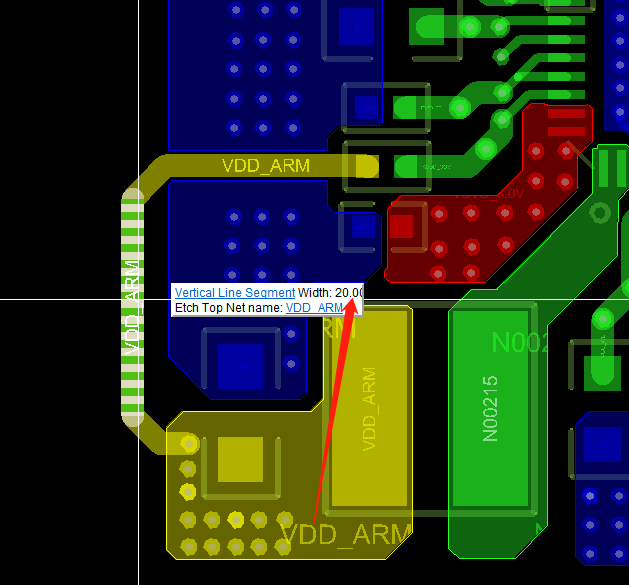

电感底部不要放置器件,以及走线也不行,自己吧底层的器件看能不能优化塞到芯片底部:注意电感跟芯片管教是属于DCDC主干道,走线肯定满足不了载流,需要铺铜处理:并且主干道器件优先放置,所有路径要尽量短,电感应该靠近管脚:建议自己分清楚原理图上的

电感底部不能放置器件,以及走线,自己优化吧电感下面的器件塞到芯片底部:布局需要改动。器件并未对齐,并且都干涉了:器件是需要整体的中心对齐放置。上述一致原因的布局问题:布局需要优化,中心对齐好,器件之间不要干涉。DCDC电源主干道的电容是要靠

1.焊盘出线应该从焊盘长方向出线,小器件应从焊盘中间出线,避免焊接问题2.地网络铺铜需要加粗和电源一样宽3.两个测试点存在飞线4.相邻大电感应朝不同方向垂直放置5.连接到9号焊盘的走线是反馈信号,不需要加粗以上评审报告来源于凡亿教育90天高

在电子行业中,PCB板的表面处理对于产品的性能和稳定性具有重要意义,它可放置电路板受到环节因素的影响,提高产品的可靠性和稳定性,但很多不良厂商会选择在表面处理工艺上偷工减料,导致PCB板质量大减,所以怎么判断?1、判断标准首先要有明确判断P

输出打孔要打在滤波电容后面2.此处不满足载流,载流是一铜皮最窄出计算的,后期自己加宽一下铜皮3.铺铜是尽量把焊盘包裹起来,这样容易造成开路4.存在多处开路和drc报错5.电感下面不要走线和放置器件6.注意中间散热焊盘上的过孔需要开窗处理7.

电感底部不能放置器件,建议自己优化下布局放置到IC芯片底部,自己修改下:器件尽量对齐:注意铜皮不要直接绘制,尽量钝角优化下:尽量能一块铺完的就一块,不要两块叠加,并且铜皮绘制尽量均匀,不要直角尖角:电感中间放置了铜皮挖空区域,铜皮重新灌下,

扫码关注

扫码关注