- 全部

- 默认排序

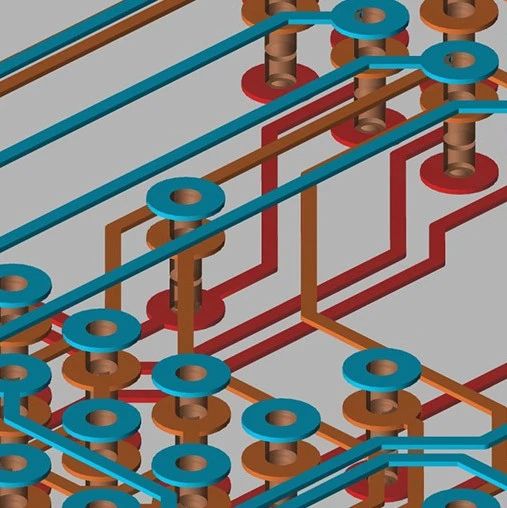

在PCB设计中,时钟信号是极为关键的敏感信号,若设置不当很容易干扰到系统稳定,电磁干扰更加严重。所以工程师必须慎重对待时钟信号,遵循其高频特性和对时序的严格要求,确保其布局布线顺利。1、减少过孔数量时钟线上应尽量减少过孔的使用,因为过孔会增

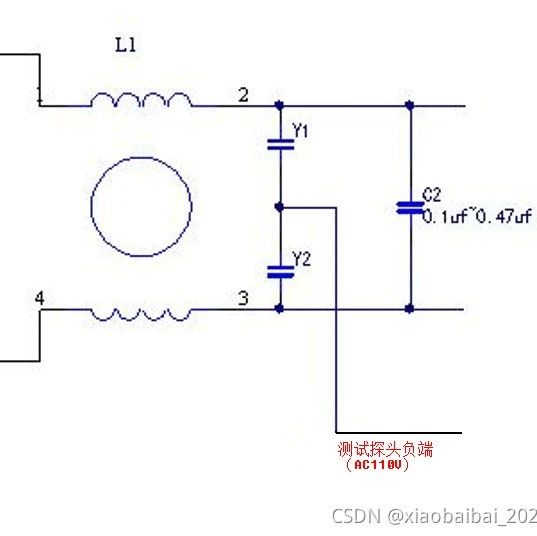

想起来曾经用的一台测试设备,由于220V的地线没有连接,测量时把板子烧坏的事情。现在记录下来警示自己。下面是一个交流220V市电的滤波器,内部原理如图: 先解释一下各元器件的作用: X电容:接在交流输入的两极,用于抑制差模干扰(电源线之间的干扰),图中的C1和C2都是X电容。Y电容:接在电源线和大地

本文要点IPC 器件间距指南旨在确保器件和电路的间距足够大,以尽量减少物理重叠和电气干扰。钻孔的间距很重要,因为钻孔的功能会受到器件间距以及 PCB 本身所用材料的影响。IPC 器件间距指南会影响电路设计,因为其中规定了许多关于导体的具体要求。IPC 是一个国际电子组织,定义了制造 PCB 的标准。

在高速PCB设计中,确保信号完整性是至关重要,而地过孔的布置,可以减少信号反射、串扰和电磁干扰(EMI),特别是在高速信号孔旁。合理的地过孔数量可显著改善信号质量,那么应该增加几个?1、最少数量对于高速信号(如频率超过1GHz),建议在信号

在电子设计中,干扰的存在一直是工程师最头痛的,干扰会导致电路发生异常,重则导致产品无法正常使用,因此,必须要巧妙甚至避免干扰问题,是许多工程师的重中之重,今天本文将谈谈单片机如何避免。需要注意的是:该方法适合有上拉电阻的单片机电路。1、精选

电子器件的噪声基本上可分为共模噪声和差模噪声,这些噪声不及时处理,很容易缩短电子产品的使用寿命,影响其正常性能,那么如何抑制差模噪声?1、电源本体降噪技术优化电路设计:在Boost等电路中,通过增大电感值和提升开关频率,可显著降低纹波电流,

电子器件的噪声基本上可分为共模噪声和差模噪声,这些噪声不及时处理,很容易缩短电子产品的使用寿命,影响其正常性能,那么如何抑制共模噪声?1、地线设计优化采用多点接地策略,减小地线阻抗,使共模电流分散流回源端,从而降低共模噪声。确保地线布局合理

随着时代发展,物联网(IoT)设备日益普及,然而随之而来是更严重的电磁干扰(EMI)问题,因此,许多大佬提议要对物联网设备做EMI测试,确保其设备本身性能稳定,降低对网络的影响。1、法规遵从性大多数国家和地区对无线设备的电磁辐射有明确的标准

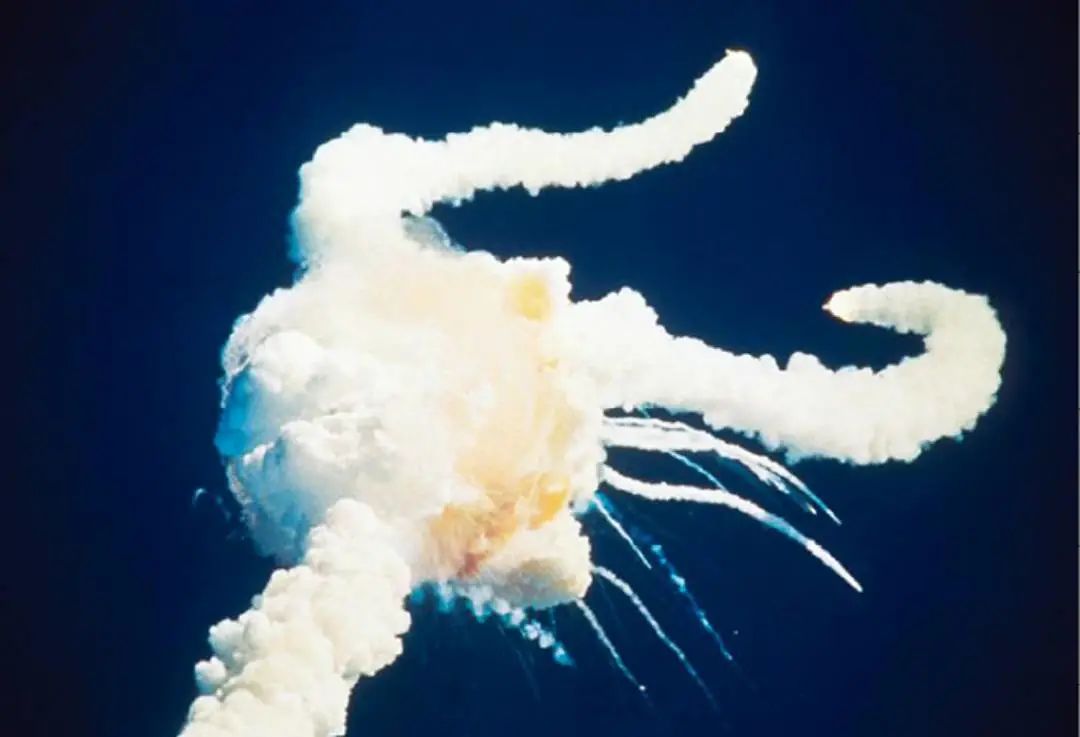

本篇主要介绍导致电子产品失效的几种主要环境应力,内容节选自《电子微组装可靠性设计(基础篇)》,本篇的思维导图如下电子产品的工作过程中,除了电载荷的电压、电流等电应力外,环境应力还包括高温和温循、机械振动和冲击、潮湿和盐雾、电磁场干扰等。在上述环境应力的作用下,产品可能出现性能退化、参数漂移、材料腐蚀

关键要点:•如何为混合信号设计布局电路板•关于限制电磁干扰(EMI)的讨论•了解可靠信号的地面和参考平面设置现在几乎在每一个新的电子设备上都能发现混合信号,拥有强大的基础对于下一代设备的开发至关重要。过去,电子产品通常由不同的单独电路板组成,每个电路板都有自己的特定功能。然而,随着设备的进一步最小化

扫码关注

扫码关注