- 全部

- 默认排序

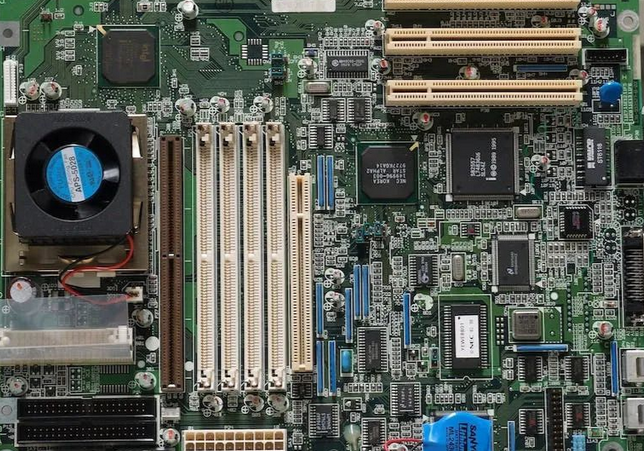

提起差分信号,很多电子工程师都不会陌生,得益于高速数字信号传输中的广泛应用,差分信号的走线在PCB设计中具有重要地位,为了确保差分信号的完整性,工程师需要遵循一些特定的规则,身为工程师的你知道有哪些规则吗?1、相对路径长度匹配差分信号对的两

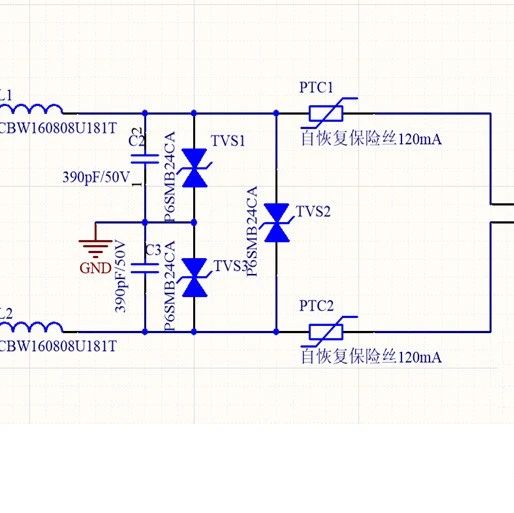

RS485电路原理图设计

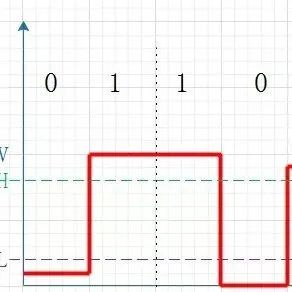

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

1、单端信号单端信号是相对于差分信号而言的,单端输入指信号有一个参考端和一个信号端构成,参考端一般为地端。2、差分信号差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法(单端信号),差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。3

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

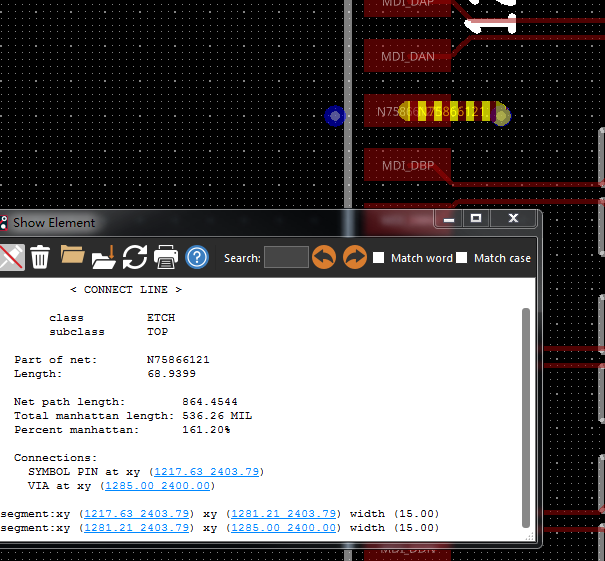

变压器上除了差分信号,其他的加粗20MIL走线:晶振尽量包地处理:RX TX以及差分组内等长没啥问题:建议机壳地与电路地之间分割2MM间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

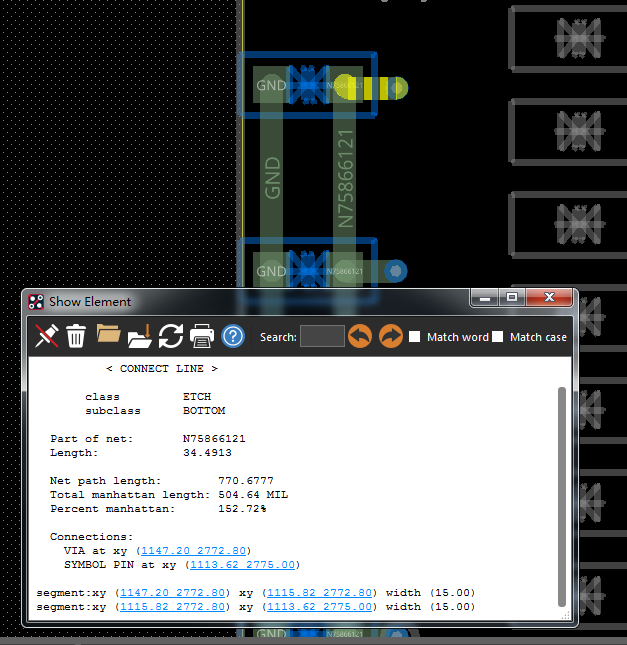

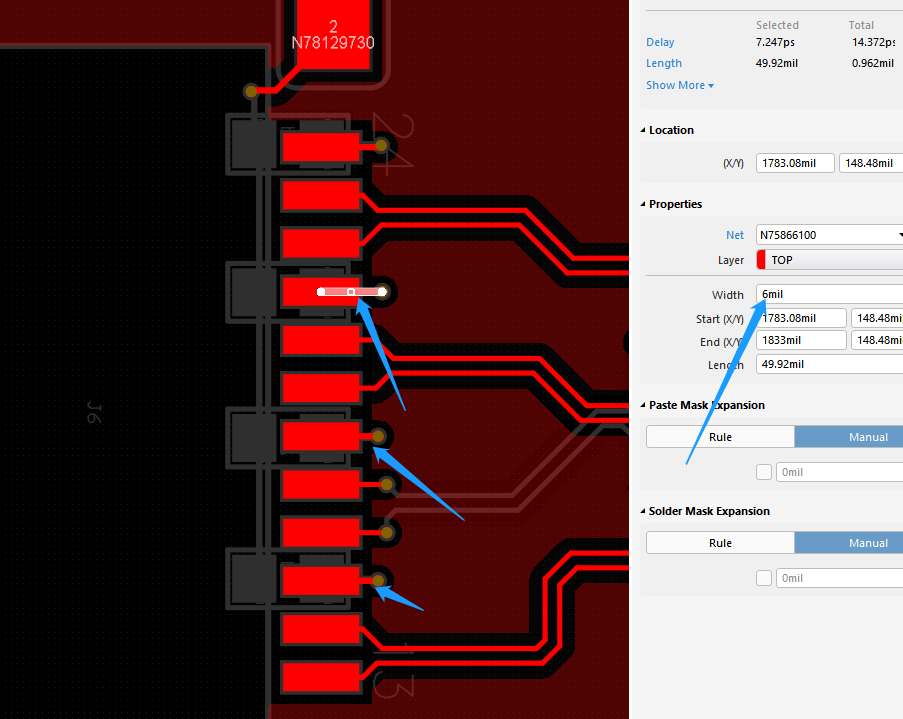

单对差分对包地50-100mil打孔差分信号走线换层在旁边打回流地过孔同层连接多余打孔多处飞线未连接差分对内长度误差5mil,设置对内等长规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

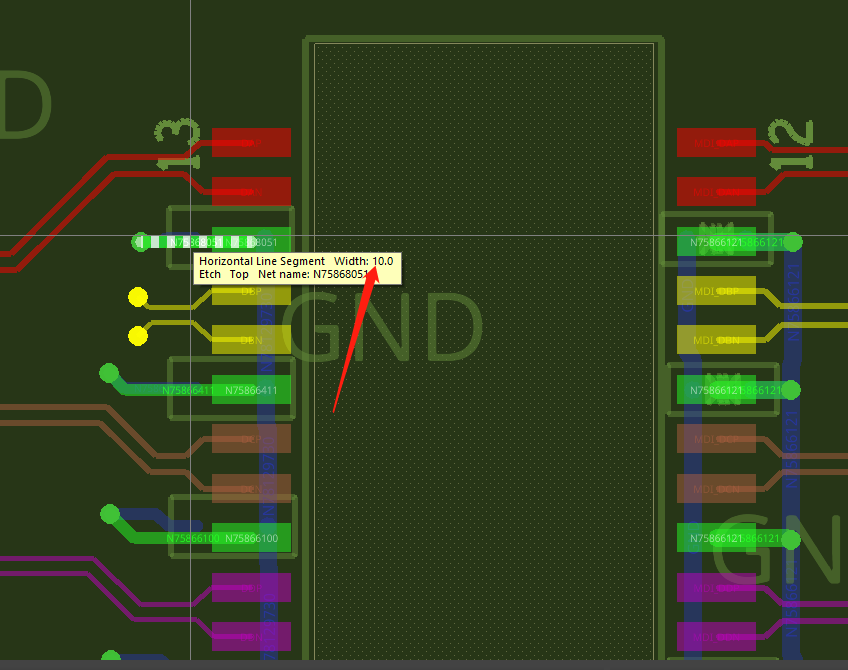

网口除差分信号外,其他信号都需要加粗到20mil2.注意网口的地分割,跨接器件旁要多打地过孔,分割间距2mm后期自己处理一下3.差分出线需要优化一下,器件可以摆放远一点,包地的线要需要均匀打上过孔4.注意差分信号需要按照阻抗线距进行走线晶振

差分信号打孔换层 注意两侧打上地过孔,缩短回流路径:注意器件尽量整体中心对齐:过孔注意间距,不要造成平面割裂:变压器上除了差分信号 其他的加粗20MIL:差分对内等长误差控制在5MIL:RX TX需要对内做等长以上评审报告来源于凡亿教育90

变压器除差分信号 其他信号20MIL:晶振注意做个包地:注意机壳地跟电路地在空间充足的情况下隔离2MM宽度:扇孔不整齐:差分以及RX TX等长没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

注意变压器除差分信号外,其他信号走线需要加粗处理2.电容尽量靠近管脚均匀摆放3.地网络需要就近打孔,连接到地平面4.注意晶振需要包地处理5.走线间距太近,后期容易造成短路,自己后期优化一下走线路径6.走线等长线之间需要满足3W规则7.时钟信

扫码关注

扫码关注