- 全部

- 默认排序

在高速串行通信系统中,差分阻抗的精确控制是实现信号完整性和降低电磁干扰的关键因素,对电子工程师来说,理想中的差分阻抗是100Ω,但由于实际布线原因,如接地屏蔽的布局,很难实现。如果要实现这个设计,工程师需要选择具有宽泛差分阻抗匹配能力的Se

在电子设备的制造与布线过程中,经常会遇见屏蔽层设计问题。问题来了,如果屏蔽层上布有电缆线,如何正确接地,降低电磁影响?下面将详细讨论这些问题。1、单点接地方案单点接地方案是最基础的接地方式,它要求所有的地线都汇聚到一个点上。这种方案在简单电

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

随着科技的快速发展,高速信号逐渐替代低速信号,成为许多电子系统的最佳选择,然而高速信号最大的缺点在于其稳定性和可靠性不如低速信号,这就需要靠走线系统来弥补。那么如何走线,保证高速信号的质量?1、屏蔽规则在高速PCB设计中,时钟等关键高速信号

EMC的屏蔽设计有哪些?

电磁兼容性(EMC)的屏蔽设计是确保电子设备在电磁环境中正常工作,同时不对其他设备产生不利影响的关键技术,在EMC设计中,屏蔽很有用,可以减少电磁场从一个区域到另一个区域的传播,那么屏蔽设计有哪些?1、屏蔽室提供低电平且稳定的环境,提高测量

在电子系统设计中,插箱作为重要的组成部分,其屏蔽性能对整个系统的稳定性和可靠性有至关重要的影响,特别是在高频工作环境下,插箱之间的电磁干扰和电磁敏感度问题变得尤为突出,所以必须采取屏蔽措施。插箱的屏蔽思路是在于减少电磁辐射和电磁干扰的传递,

在电磁兼容性(EMC)与屏蔽设计领域时,很多工程师尽量确保电子设备面授外部电磁干扰,以及防止内部电磁辐射泄露,其中有一条原则是:尽量使机箱内的电缆原理缝隙和孔洞,这是为什么?今天将针对这个问题进行简短探讨,希望对小伙伴们有所帮助。1、磁场伴

在变压器的设计与制造中,磁芯算是其中的核心部件,有许多工程师好奇,如果磁芯有不同形状,是否会对变压器性能有一定影响?本文将针对该问题进行探讨,希望对小伙伴们有所帮助。1、圆柱形磁芯优点:EMI屏蔽效果好:圆柱形磁芯由于其封闭的形状,对电磁干

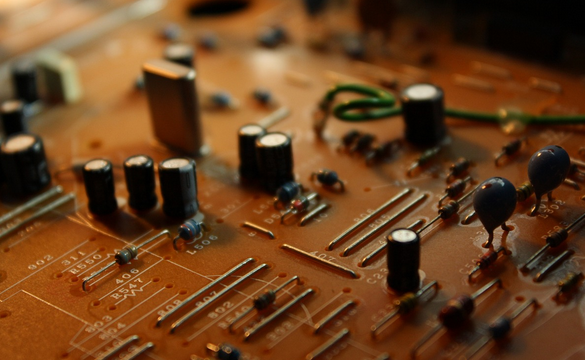

在高速PCB设计中,我们经常会看见工程师在电路板上铺铜,确保电路板的性能是稳定且可靠的,但有没有更深的原因?一起来看看吧!1、EMC屏蔽与防护大面积的地(GND)或电源(VCC/VDD)铺铜可以有效屏蔽外部电磁干扰,保护内部信号不受影响。特

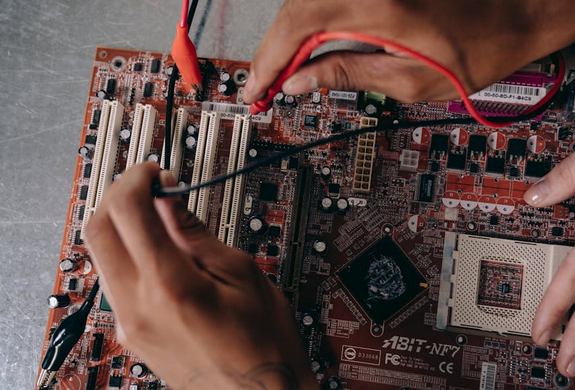

电磁兼容性问题在现代电子设备中屡见不鲜,快速准确地定位并解决这些问题对于设备的稳定性和可靠性至关重要。本文将分享五个小技巧,可帮助工程师针对性解决电磁兼容故障!1、辐射发射超标处理检查设备外壳屏蔽性能,必要时加强屏蔽。拔掉不必要的电线和电源

扫码关注

扫码关注