- 全部

- 默认排序

门禁系统受到误报和尾随等问题的困扰。Hakimo 是一家新公司,其应用深度学习的概念来减少误报和尾随,并使访问控制更加准确。来自访问控制系统的误报等问题耗费了全球安全运营中心 (GSOC) 的操作员花费大量的时间和精力。这是浪费他们可以用来

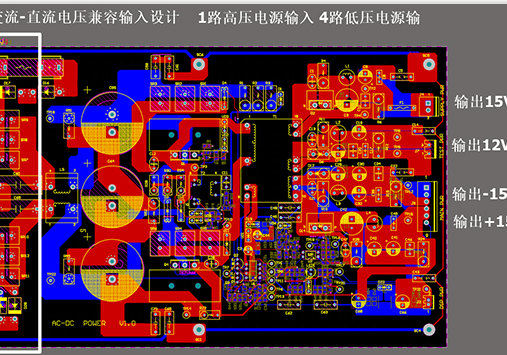

熟悉电路设计的小伙伴们都知道,在电源设计中,散热和电磁干扰(EMC)是困扰工程师的最大难题,以LED电源电路问题最甚。一般来说,LED电源最大的特点是在导通时,电压低、电流大;在关断时,电压高、电流小,因此功率半导体器件上所产生的的损耗很小

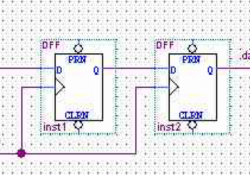

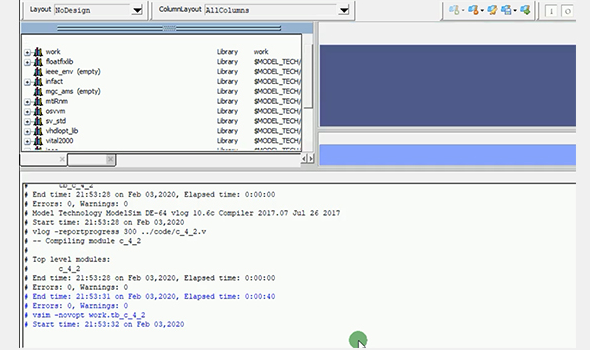

同步时序电路和异步时序电路是数字电路的重要内容,也是小白学习数字电路时重点学习的电路设计课程之一,但如果我们遇见异步时钟域数据同步问题,我们该怎么办?处理跨时钟域问题的核心在于要保证下级时钟对上级数据采样的setup时间或hold时间满足要

机器学习等计算密集型技术的发展带来了高碳足迹,并加剧了气候变化。机除了快速增长之外,还有不断扩大的绿色人工智能工具和技术组合,以帮助抵消碳排放并提供更可持续的发展道路。根据微软和艾伦人工智能研究所,以及希伯来大学、卡耐基梅隆大学和人工智能社

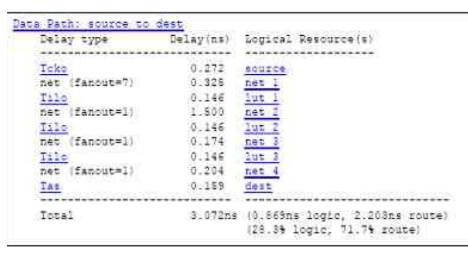

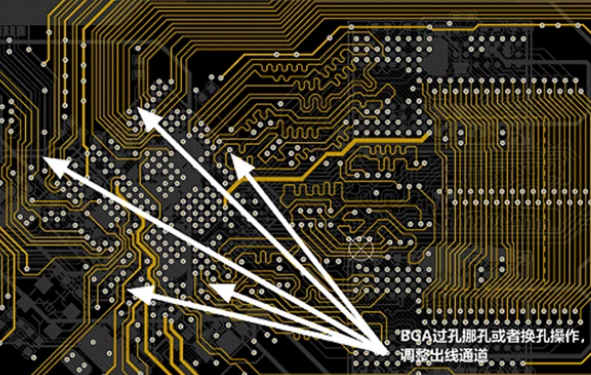

时序性能是FPGA设计最重要的技术指标之一,在项目设计中很多人经常会遇见时序性能差的现象,但不知道该如何解决。造成时序性能差的根本原因有很多1、布局太差如图所示:该图是布局太差的时序报告示意图,其中附加的周围约束为3nm,实际周期为3.02

在FPGA设计时,我们总会遇到各种各样的设计难题,并发愁如何解决,所以小编将搜集网络上九个小白最头疼的FPGA设计问题,并进行回答,希望对小白有所帮助。1、如何控制XST插入buffer?①用buffer_type约束,具体使用方法在XST

很多小白在进行软硬件测试时 都会遇见多种问题,如果是软件测试只需通过调试解决BUG来进行,过程繁琐但单一;但硬件测试极大地考验小白的基础知识及实践能力,这也造成很多小白轻松进行软件测试,但对于硬件测试却束手无策,所以硬件测试中遇到问题该如何

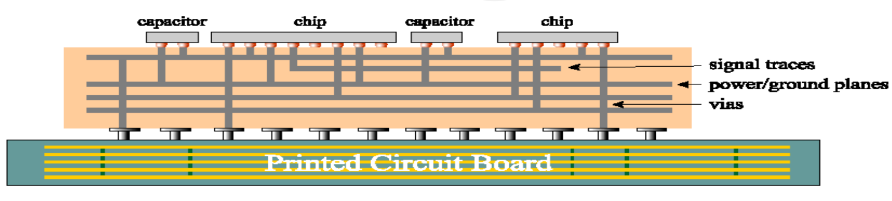

信号完整性测试(SI)是硬件测试的常见内容之一,也是通信/无线工程师需要重点了解的基础内容之一,但有很多小白遇见SI问题却不知道如何解决,所以本文将重点分享常见的信号完整性测试(SI)问题及解答内容。1、反射产生的原因一般来说,反射产生的原

多年来,数据中心的出现与数据消费的增长和云计算的迅速采用成正比。公司正积极利用物联网 (IoT)、工业 4.0 和新时代技术来提高生产力和工作效率。因此,全球组织在利用大数据和数据分析的优势进行数据管理方面表现出积极性。数据中心已成为计算、

小白初学电机驱动进行实验,首先接触到的电机必然是步进电机,但在使用过程中必然出现多种问题却不知道该如何解决,例如:如何克服两相混合式步进电机的振动和噪声?等等,所以本文将一一解决这些问题。1、如何克服两相混合式步进电机的振动和噪声?步进电机

扫码关注

扫码关注