- 全部

- 默认排序

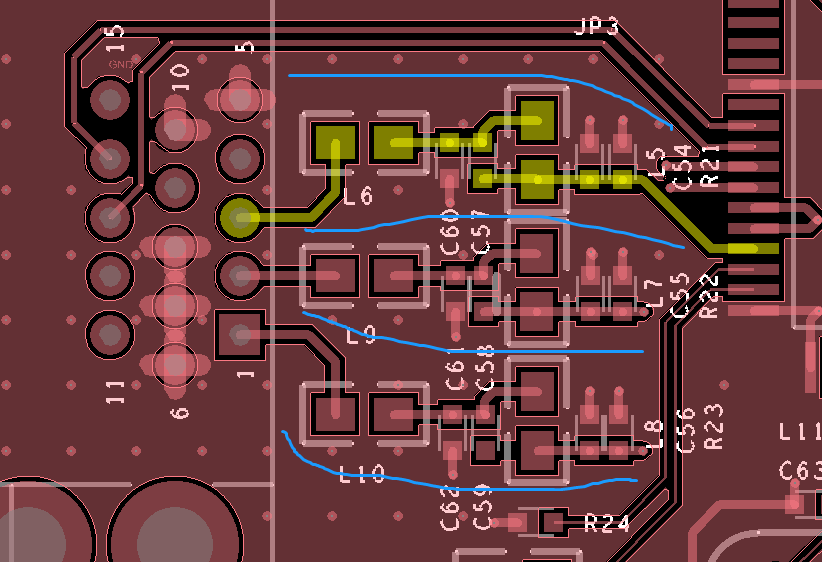

模拟信号需要一字型布局,单根包地处理2.晶振需要走内差分处理3.跨接器件旁边尽量多打地过孔,间距最少1mm,有器件不满足可以忽略,其他地方要尽量满足4.差分走线要尽量耦合5.百兆出差分信号外,其他信号都需要加粗到20mil6.模拟信号需要一

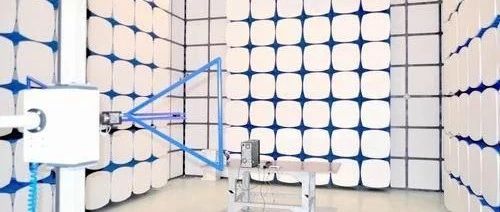

1为什么要对产品做电磁兼容设计?答:满足产品功能要求、减少调试时间,使产品满足电磁兼容标准的要求,使产品不会对系统中的其它设备产生电磁干扰。2对产品做电磁兼容设计可以从哪几个方面进行?答:电路设计(包括器件选择)、软件设计、线路板设计、屏蔽结构设计、信号线/电源线滤波设计、电路接地方式设计。3在电磁

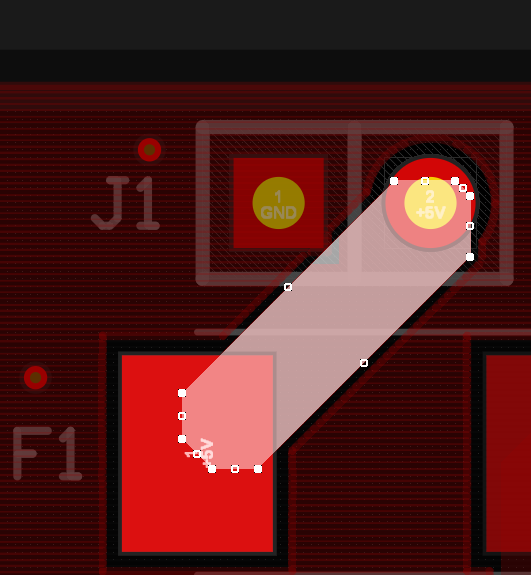

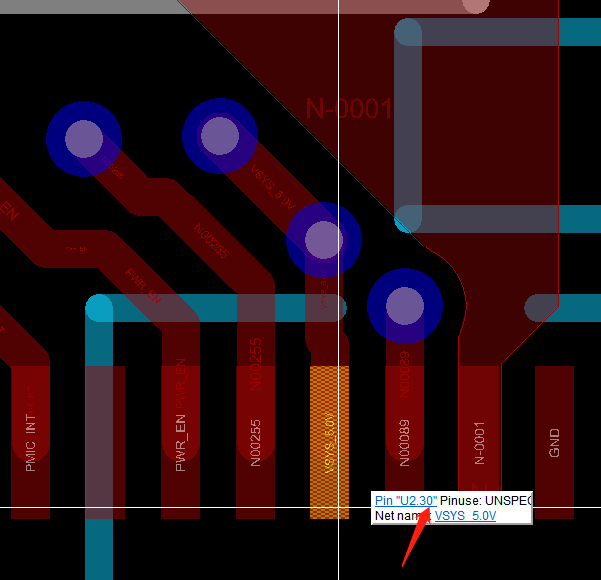

电源铜皮尽量铺工整一点,并且加宽铜皮宽度满足载流大小:此电源输入主干道通道比较长,建议是否可以调整布局,缩短主干道路径:输出主干道是否可以加宽铜皮宽度:反馈信号直接走线连接,不要打孔连接电源平面:5V电源有这种瓶颈的地方,自己优化加宽:模拟

跨接器件旁边尽量多打地过孔,间距最少1.5mm,有器件的地方可以不满足,其他地方尽量满足2.网口差差分外,其他信号需要加粗到20mil3.差分线可以在优化一下4.滤波电容靠近管脚摆放,器件可以放底层5.走线与焊盘同宽,拉出来再进行加粗6.晶

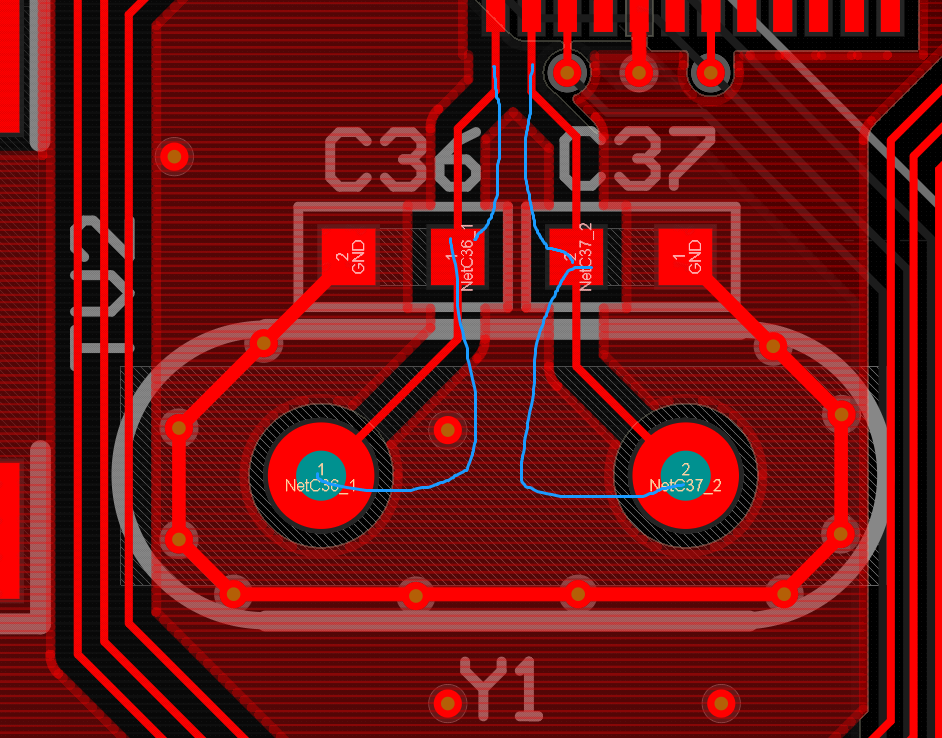

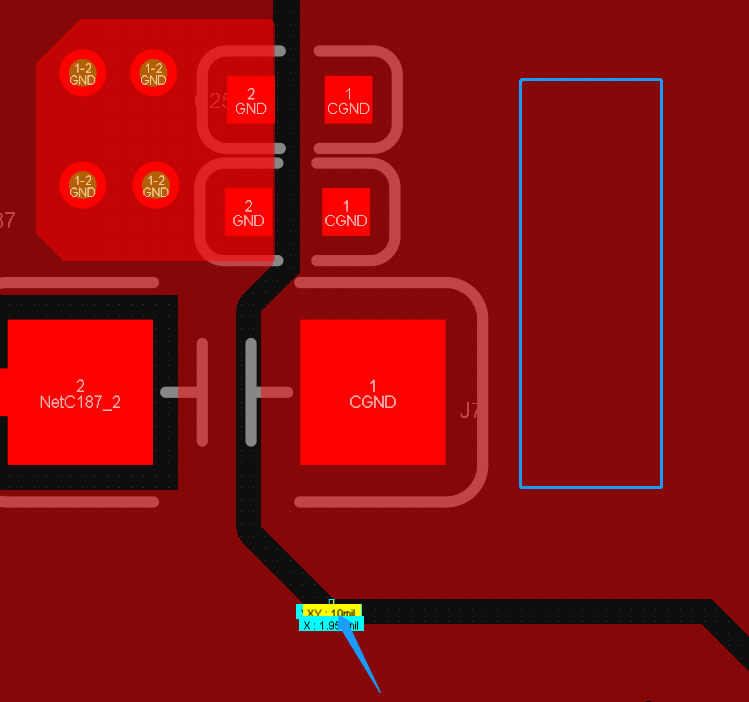

晶振走内差分需要再优化一下2.地分割间距最少1mm,建议2mm,有器件的地方可以不满足3.反馈信号走线需要加粗4.电感中间挖空就不要有铜皮5.输出打孔要打在电容后面6.注意过孔尽量盖油,不要上焊盘以上评审报告来源于凡亿教育90天高速PCB特

此处不满足载流2.此处存在开路3.输出打孔要打在滤波电容后面5.反馈线要从滤波电容后面取样,走10mil即可6.电感所在层的内部需要挖空处理,背面尽量不要放置器件7.电源网络需要再底层铺铜进行处理,剩下的地方铺地以上评审报告来源于凡亿教育9

芯片中间的散热焊盘两面都需要开窗过孔不要打在焊盘上,调整一下走线不要从电阻中间穿过电容靠近管脚放置跨接器件旁边尽量多打地过孔,间距最少1.5mm,有器件的地方可以不满足,其他地方尽量满足tx和rx之间尽量用一根20mil的地线分割开来以上评

跨接器件旁边尽量多打地过孔,间距最少1mm,有器件的地方可以不满足2.地网络直接就近打孔,走线不要从小器件中间穿,容易造成短路3.等长存在误差报错4.注意等长线之间需要满足3W间距5.注意一下此处是否满足载流6.器件摆放不要干涉一脚标识7.

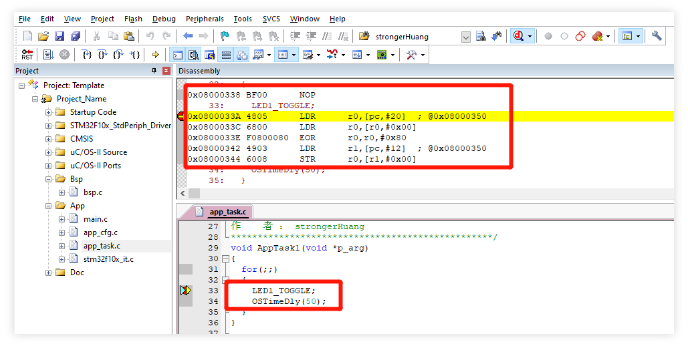

最近又看到关于【嵌入式开发有没有必要学汇编】的话题。我觉得学汇编有学汇编的道理,不学也有不学的道理,这个很正常。不同的人有不同的观点,讨论激烈也很正常。现在可能很少看到汇编程序了,但单片机的启动文件、RTOS底层等一些地方,依然还有汇编代码

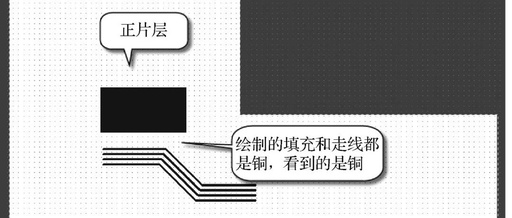

1、层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。2、正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。图8-32 正片

扫码关注

扫码关注