- 全部

- 默认排序

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

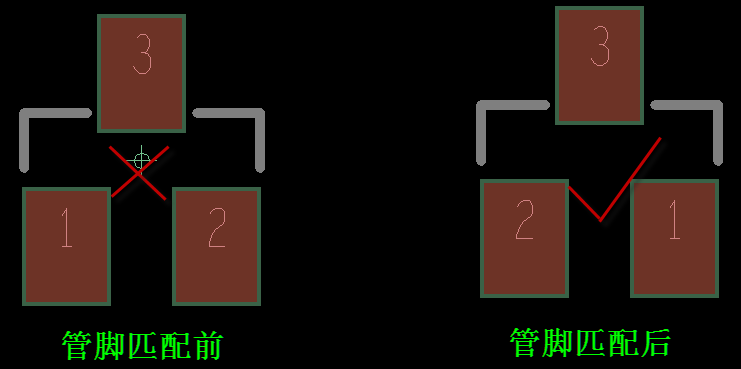

答:在制作封装时,经常会碰到要进行封装管脚匹配,特别是3极管类型封装,特别容易将管脚排序做错。以下给大家介绍三极管管脚排序的方法:第一步,打开原理图,找到对应的器件,查看器件的管脚排序,如下图,分析图示可知,1脚为E极,2脚为B极,3脚为C极,如图4-119所示

在设计原理图库原件的时候,原件过小。但是器件管脚长度过长,显得器件很不协调。第一步:执行快捷键命令PP放置管脚,如图1所示。图1第二步:双击管脚,弹出属性框,在PIN length处修改既可。如图2所示。图2

AD在制作原器件封装的时候旋转原器件管脚的方法,其实是有俩种的。第一种:选中双击管脚弹出属性编辑界面,如图1所示。在Rotation的选项下既可选中管脚的角度。图1第二种:选中管脚在拖动的状态下按空格键既可完成角度旋转。

很多工程师发愁高频PCB布局布线,若是画板不好,将直接影响到电路性能和稳定性,所以必须要在这方面下功夫,那么有没有方法可以更快更高效?或许你可以关注这四个要点!1、减少高频电路器件管脚件的引线层间交替在高频电路中,器件管脚间的引线层间交替过

为什么我用AD画原理图时候,把两个器件引脚放一起然后拉开,他们之间却没有引线呢?是不是需要哪里设置还是其他的?

17.4和17.2不一样吗?按照视频讲解的去做 按住ctrl 选中的管脚会拖动 而且我进入这个package里面这个package properties是无法点击的 也不像视频说的双击左键会出来 属性框

扫码关注

扫码关注