- 全部

- 默认排序

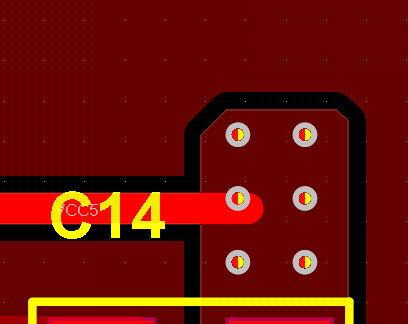

在进行阻抗匹配的时候我们可以在电阻源端放置一个串联端接电阻,但是有时候受到空间的限制可能会把电阻摆的稍微远一点,那么这个时候大家可能会有疑问,电阻离发送端远一点或者电阻放置在接收端,那么电阻还能消除传输线的反射吗?下面我们一起来验证一下!1

在电磁兼容性设计中,信号反射是电子工程师的重要考虑因素之一,特别是在高速数字系统中,信号反射可导致多种问题,如过冲、下冲和振铃,针对这些问题如何分析,并制作相关的电路设计?首先,这些问题的发生,原因在于是由信号在传输线上传播时遇到阻抗不匹配

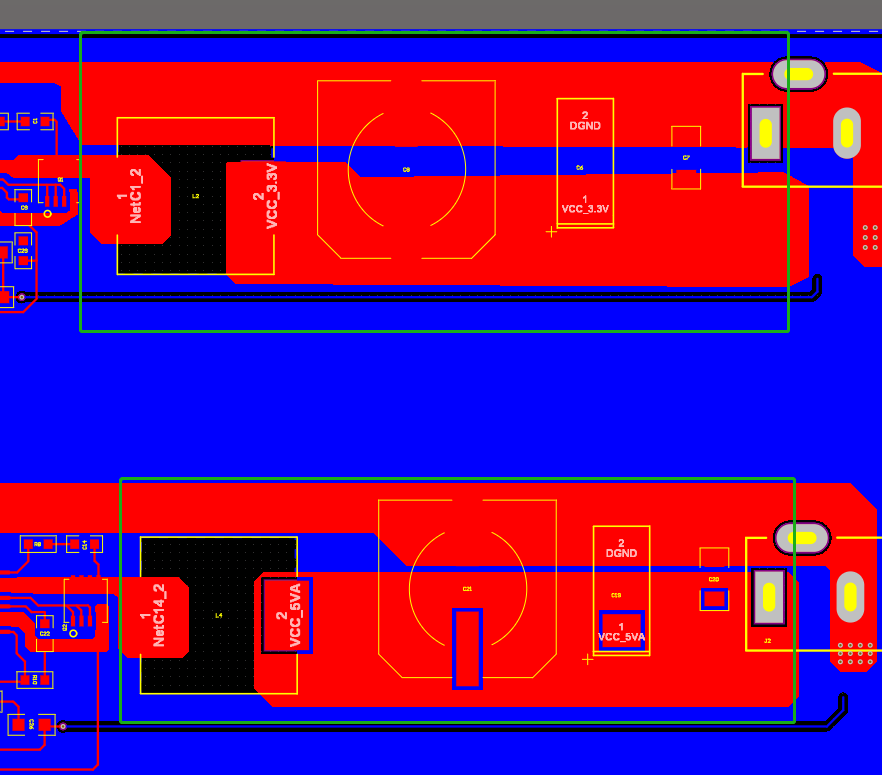

注意4层板不需要用埋盲孔2.反馈信号需要加粗到10mil,注意焊盘出线规范3.注意变压器负片层挖空处理,地分割注意规范4.注意丝印调整尽量不要干涉器件丝印以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

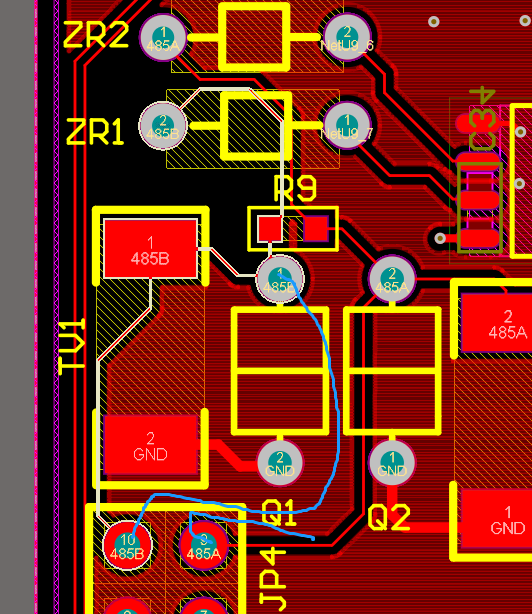

注意485需要走类差分形式2.跨接器件旁边要尽量多打地过孔,间距要最少要1.5mm3.差分对内等长凸起高度不能超过线距的两倍4.差分出线要尽量耦合5.模拟信号需要加粗处理6.反馈信号需要加粗到10mil7.注意数据线之间等长需要满足3W规则

2019年8月9日,华为正式发布鸿蒙系统,当时承受了许多偏见,其中最大的反对莫过于“套壳安卓”,然而经历四年的迭代升级,鸿蒙系统已经有底气说出要与安卓完全脱离。之前鸿蒙系统生态系统仍未建设完全,为了迅速扩大用户规模,不得不采取兼容安卓的策略

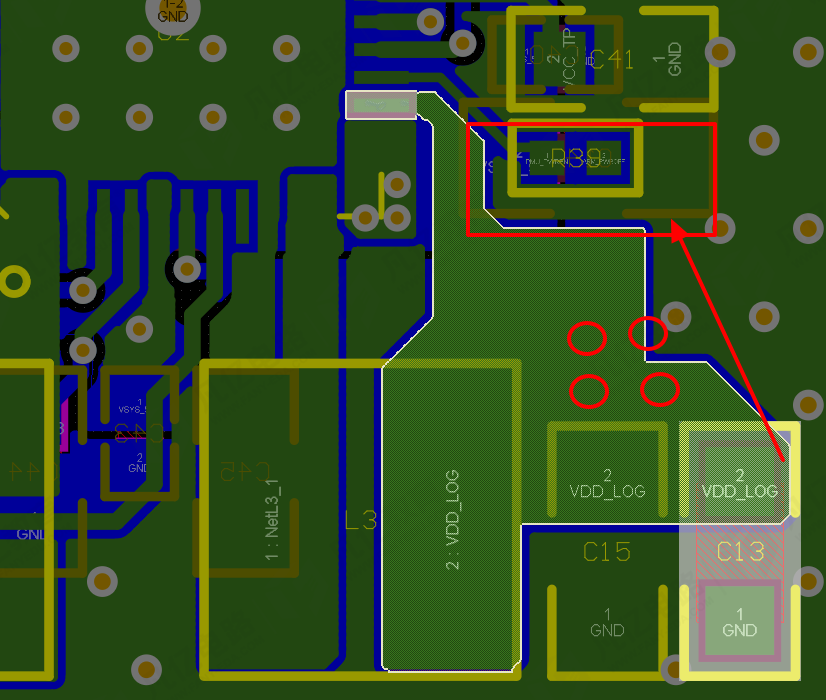

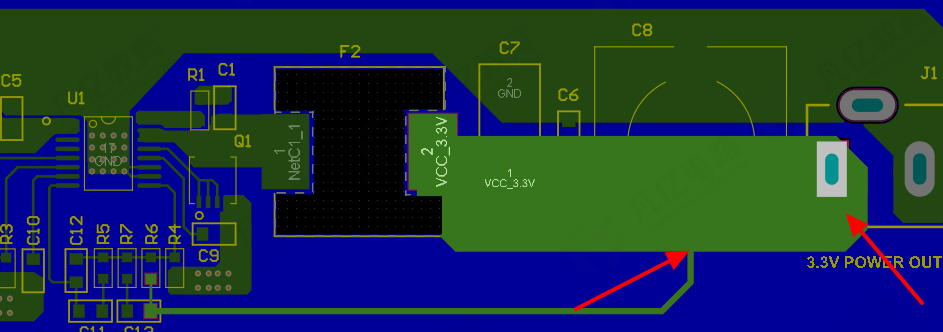

电容布局布线错误,此脚是反馈信号,电容应靠近管脚放置电源输出端打孔多处电源走线需要加粗走线不能从同层器件下穿过以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ite

运算放大器(简称:运放)是电子电路中非常重要的元件之一,具备高放大倍数、高输入电阻、低输出电阻等优点,被广泛应用在各大模拟电路中,然而在使用过程中却出现了振荡自激现象,那么如何查找原因,并找到解决方法?一、常见原因分析1、负反馈电路设计不当

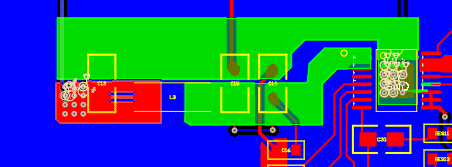

绿色的铜皮是修改后没有重铺的铜皮属性要选择这一项这个vcc12v的走线要加粗处理最好铺铜连接这里要出线后在连接dcdc需要单点接地输入输出主干道要铺铜连接这个反馈不要走电感下面而且要从最后一个电容处拉出来散热过孔两面都要做开窗处理以上评审报

电源主干道的器件注意整体中心对齐:此处输入电源主干道器件完全没有中心对齐放置:铺铜不要直角,尽量都钝角,优化下,类型情况的都自己检查修改下,不一一截图出来:电感当前层内部需要挖空处理:反馈信号没有连接上,连接到最后输出电源处:铜皮没有赋予网

反馈信号要连到电源最末端电容要按照先大后小原则摆放要求单点接地,整路电源都要连接到一起,在一个点打孔接地以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.t

扫码关注

扫码关注